Don't wanna be here? Send us removal request.

Text

Agnisys: Reshaping Semiconductor Design with Specification Automation and Advanced Register Modeling

In the fast-paced realm of semiconductor design and verification, Agnisys stands as a beacon of innovation, pushing boundaries with its cutting-edge solutions in specification automation and register modeling. This article delves into the intricacies of Agnisys' UVM Register Layer, UVM Register Model, and the influential Register Model Generator, spotlighting their transformative impact on the semiconductor industry.

Agnisys' UVM Register Layer: A Catalyst for Verification Efficiency

At the core of Agnisys' offerings lies the UVM Register Layer, an integral component in the Universal Verification Methodology (UVM). This layer plays a pivotal role in the verification process by providing a systematic approach to verify and validate register-based designs.

A standout feature of Agnisys' UVM Register Layer is its capacity to automate the generation of UVM-based register verification environments. This not only expedites the verification process but also ensures uniformity and precision across the design.

UVM Register Model: Precision in Design Verification

Agnisys' UVM Register Model further enhances the verification process by offering a robust and efficient means to represent and verify register designs. This model serves as a comprehensive abstraction of the register specification, capturing its behavior and interactions within the system.

With UVM Register Model, engineers seamlessly integrate register verification into their overall strategy, fostering improved design reliability and a quicker time-to-market, crucial elements in addressing the escalating complexity of semiconductor designs.

Register Model Generator: Empowering Design Creativity

The Register Model Generator from Agnisys emerges as a powerful tool, granting engineers the capability to automatically generate register models from specifications. This significantly reduces manual efforts in creating register models, enabling designers to concentrate on critical aspects of the design process.

The efficiency gains provided by the Register Model Generator are particularly noteworthy in large-scale projects where the sheer volume of registers can be overwhelming. By automating this facet of the design process, Agnisys empowers design teams to navigate complex projects with heightened agility and precision.

Agnisys' Impact on the Semiconductor Industry

Agnisys' commitment to innovation and excellence has positioned the company as a trailblazer in the semiconductor industry. The tangible applications of their tools are evident in the streamlined design and verification workflows embraced by leading semiconductor companies globally.

By simplifying and automating intricate processes such as register modeling, Agnisys has substantially contributed to reducing development cycles and mitigating the risk of errors. This, in turn, directly impacts the overall efficiency and competitiveness of semiconductor design projects.

Future Prospects and Continuous Innovation

As technology advances at an unprecedented pace, Agnisys remains at the forefront of innovation, proactively addressing the evolving needs of the semiconductor industry. The ongoing enhancement of their tools and the introduction of cutting-edge features underscore their commitment to empowering engineers and designers.

In conclusion, Agnisys has solidified its position as a force reshaping semiconductor design through specification automation and register modeling. The industry can count on Agnisys to provide indispensable tools that enhance efficiency, accuracy, and contribute to the success of intricate design projects. As the semiconductor landscape evolves, Agnisys stands ready to play a pivotal role in shaping the future of semiconductor design and verification.

0 notes

Text

Precision Unleashed: Mastering ASIC Design with SystemRDL Parser, RAL, UVM Testbench, and UVM Register Model Integration

Introduction: In the ever-evolving realm of ASIC design, the pursuit of precision is not just a preference—it's a mandate for engineering excellence. This in-depth exploration embarks on a journey through the intricate corridors of ASIC design, unveiling the strategic integration of a SystemRDL parser, the Register Abstraction Layer (RAL), and the symbiotic relationship with the Universal Verification Methodology (UVM) testbench and UVM Register model. Real-world UVM case studies serve as beacons, illuminating the transformative power of this comprehensive integration.

SystemRDL Parser: The Maestro of Precision: At the epicenter of precision-driven ASIC design stands the SystemRDL parser—a maestro orchestrating the intricate dance of registers. This automated parsing tool isn't just a facilitator; it's a strategic enabler. Its role extends beyond simplifying the verification process; it introduces an unparalleled level of consistency that is fundamental to the success of ASIC designs in an environment characterized by increasing complexity.

UVM Testbench: Automation's Synergistic Partner: Automation within the SystemRDL-driven RAL framework extends its influence into the UVM testbench. This partnership liberates designers from the shackles of manual efforts, mitigating the risks associated with human errors. The seamless alignment between the UVM testbench and register specifications, coupled with strategic automation, forms the bedrock of precision in ASIC design.

UVM Register Model: Elevating Sophistication: The UVM Register model, esteemed as a pinnacle of sophistication, seamlessly integrates into the ensemble. This integration involves a meticulous translation process, ensuring that any changes in register specifications gracefully propagate through the UVM testbench. The resulting harmony enhances the coherence of the entire project, providing a robust foundation for ASIC designs to flourish.

Precision in Action: Real-world UVM Case Studies: The litmus test for precision lies in the real-world crucible. UVM case studies emerge as living proof of how the SystemRDL parser, UVM testbench, and UVM Register model collaborate seamlessly. Envision an ASIC design landscape with diverse IP blocks, each with unique register specifications. These case studies serve as vivid illustrations, demonstrating precision, adaptability, and customization in action, showcasing the dynamic nature of this holistic approach in addressing real-world design complexities.

Strategic Solutions for Precision Challenges: Precision engineering is not without its challenges. While automation serves as a potent tool, addressing challenges strategically is imperative. Diverse register specifications across different IP blocks demand customization and flexibility in SystemRDL parsing tools. Robust error-handling mechanisms become the guardians of precision, detecting and rectifying discrepancies to ensure an uninterrupted flow from design to verification.

Conclusion: Precision Redefined for ASIC Design Mastery: In conclusion, the journey toward precision in ASIC design transcends aspirations—it demands a strategic orchestration of tools and methodologies. The integration of an automated SystemRDL parser, seamlessly interwoven with the UVM testbench and UVM Register model, represents the epitome of this precision-driven approach. Real-world UVM case studies not only validate its efficacy in expediting the verification process but also underscore its pivotal role in elevating the overall quality of ASIC designs. As the semiconductor industry propels forward, embracing this comprehensive integration becomes not just advantageous but indispensable for mastering the intricacies of ASIC design in an ever-evolving market.

0 notes

Text

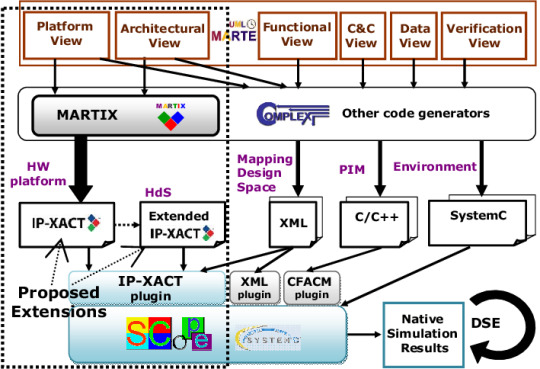

Revolutionizing Hardware Development: A Deep Dive into IP-XACT, UVM Register Model, and SystemRDL Compiler

In the ever-evolving landscape of hardware design, the quest for efficiency, precision, and seamless integration is unending. This article delves into the intricacies of three indispensable components that have become keystones in modern hardware development: IP-XACT, UVM Register Model, and the SystemRDL Compiler. By exploring the nuanced details of each, we aim to unravel their transformative impact on the hardware design process.

1. IP-XACT: The Standard for Streamlined IP Integration

Decoding IP-XACT:

IP-XACT, or Intellectual Property eXchange – Accurate Creation Tool, emerges as an IEEE standard designed to standardize the integration of intellectual property (IP) within electronic design automation (EDA). At its core, IP-XACT serves as a lingua franca, providing a standardized language for describing, packaging, and seamlessly integrating IP blocks across diverse design tools and environments.

In-Depth Features of IP-XACT:

Metadata Mastery: IP-XACT's prowess lies in its ability to encapsulate detailed metadata descriptions of IP blocks. This includes a comprehensive breakdown of the IP's functionality, configuration options, and usage constraints. This metadata not only acts as a blueprint for understanding the intricacies of the IP but also serves as a robust documentation framework, enhancing collaboration among design teams.

Interoperability Enhancement: The standardization brought about by IP-XACT plays a pivotal role in enhancing interoperability among different EDA tools. By providing a common language for IP descriptions, it eradicates compatibility hurdles, allowing designers to seamlessly integrate IP components from various sources. This not only expedites the design process but also mitigates risks associated with integrating disparate IP blocks.

Configurability for Unmatched Flexibility: IP-XACT empowers designers by allowing them to specify configurable parameters for IP blocks. This configurability injects a level of flexibility into the design process, promoting reusability and adaptability. Designers can tailor IP blocks to meet specific project requirements, ushering in a new era of versatile and customizable hardware designs.

Real-World Application:

Consider a scenario where a design team is tasked with integrating a complex IP core into their project. The absence of a standardized language could lead to confusion and errors during integration. IP-XACT acts as a unifying force, providing a consistent framework that streamlines integration efforts and ensures a harmonious design flow.

2. UVM Register Model: Precision in Register Verification

Navigating UVM Register Model:

Within the expansive domain of hardware verification, the Universal Verification Methodology (UVM) stands as a beacon of reliability. UVM Register Model, a critical component within UVM, offers a systematic approach to model and verify hardware registers, ensuring precision and efficiency in the verification process.

Key Features of UVM Register Model:

Abstract Representation for Conceptual Clarity: UVM Register Model introduces the concept of abstract representations of hardware registers. This abstraction serves as a conceptual bridge, allowing designers to grapple with complex register structures at a higher level of abstraction. The result is a more intuitive and streamlined verification process.

Uniform Access Mechanism for Consistency: A standout feature of UVM Register Model is its establishment of a consistent mechanism for accessing registers. This uniformity ensures that register interactions during the verification process adhere to a standardized protocol, minimizing the likelihood of errors and discrepancies.

Automatic Code Generation for Efficiency: UVM Register Model takes efficiency a step further by automating the generation of code for register access. This automation not only reduces manual effort but also decreases the risk of errors associated with manual coding. Verification engineers can focus their efforts on strategic aspects of the verification process, confident in the accuracy of the generated code.

Real-World Application:

Imagine a design project involving a myriad of registers that require meticulous verification. UVM Register Model simplifies this process by offering an abstract representation, ensuring uniform access, and automating code generation. This not only expedites the verification phase but also elevates the overall accuracy of the verification environment.

3. SystemRDL Compiler: Crafting Clear and Concise Register Descriptions

Unveiling SystemRDL Compiler:

In the tapestry of hardware design, SystemRDL, or Register Description Language, emerges as a specialized language designed explicitly for describing registers and memory-mapped registers. The SystemRDL Compiler translates these descriptions into models compatible with various verification environments, seamlessly integrating with UVM.

Key Attributes of SystemRDL Compiler:

Human-Readable Syntax for Intuitive Descriptions: A standout feature of SystemRDL is its commitment to a human-readable syntax. This syntax streamlines the process of describing intricate register hierarchies and configurations, fostering clear communication among design teams. The readability of SystemRDL becomes a catalyst for efficient collaboration.

Parameterization for Versatility and Reusability: SystemRDL empowers designers with the ability to parameterize register descriptions. This means that register models can be easily modified and reused in different segments of the design. Parameterization adds a layer of versatility, allowing designers to adapt register models to specific project requirements without resorting to extensive rework.

Seamless Integration with UVM: The SystemRDL Compiler seamlessly integrates with UVM, forming a cohesive bridge between register description and the verification environment. This integration ensures that the register models described in SystemRDL effortlessly fit into the broader verification framework, creating a unified ecosystem for design and verification teams.

Real-World Application:

Consider a design scenario where a team needs to describe a complex set of registers with clarity and conciseness. The SystemRDL Compiler, with its human-readable syntax and parameterization capabilities, simplifies this task. The seamless integration with UVM ensures that the described register models seamlessly fit into the broader verification framework, fostering a streamlined and efficient development process.

In Conclusion: Navigating the Landscape of Modern Hardware Design

In the dynamic and complex landscape of modern hardware design, the triumvirate of IP-XACT, UVM Register Model, and the SystemRDL Compiler emerges as a formidable force. These components, each playing a distinct yet interconnected role, contribute to the efficiency, reusability, and accuracy of contemporary hardware designs.

As engineers and designers navigate the intricacies of hardware development, understanding and harnessing the power of IP-XACT, UVM Register Model, and the SystemRDL Compiler become not just best practices but imperatives for success. The ability to seamlessly integrate IP, precisely model registers, and describe registers in a clear and concise manner lays the foundation for efficient and error-free hardware designs.

In an era where technology advances at an unprecedented pace, these components serve as beacons, guiding hardware designers towards a future where complexity is tamed, and innovation thrives. The revolution in hardware development is not just on the horizon; it is here, propelled by the transformative capabilities of IP-XACT, UVM Register Model, and the SystemRDL Compiler.

0 notes

Text

PSS Data Model and Tools: A Revolution in Clock Domain Crossing Optimization

In the ever-evolving landscape of hardware design, the integration of the Property Specification Language (PSS) data model and advanced tools marks a revolutionary stride, particularly in addressing the intricate challenges associated with the automatic handling of register clock domain crossings (CDCs). This article delves into the transformative impact of PSS, unraveling the intricacies of its data model and spotlighting the capabilities of its tools in not just navigating, but elevating the design process.

Unpacking the PSS Data Model

At the heart of this transformation lies the PSS data model, an adaptive framework empowering designers to articulate complex design intent, constraints, and properties with utmost clarity and precision. PSS offers a high-level abstraction, acting as the linguistic bridge between design intent and flawless execution, paving the way for an efficient and expressive design journey.

Navigating Design Complexity with PSS Tools

Register Description Excellence

PSS tool shine brightly in the realm of register description, providing designers with an intuitive platform to express intricate register maps and associated properties. The declarative nature of PSS facilitates a clear and concise specification, laying a robust foundation for subsequent design stages.

Automatic Handling of CDCs: A Synchronized Symphony

Clock domain crossings, a notorious challenge in digital design, find a natural adversary in PSS. Leveraging temporal assertions, PSS tools empower designers to define precise relationships between signals in different clock domains. This, combined with sophisticated scenario modeling, orchestrates a synchronized symphony, automatically handling CDCs and fortifying the overall design robustness.

Temporal Assertions: Precision Redefined

PSS allows designers to articulate temporal assertions with unparalleled precision, defining temporal relationships between signals crucial for clock domain crossings. This precision acts as a sentinel, ensuring synchronized data transfer and elevating the overall reliability of the design.

Scenario Modeling: A Holistic Design Canvas

Beyond temporal assertions, PSS excels in scenario modeling, providing designers with a panoramic view of the design's behavior. This capability proves indispensable in proactively identifying and addressing potential issues related to register CDCs, fostering a holistic and proactive design approach.

PSS Tools in Action: Orchestrating Design Symphony

Automated Register Generation

PSS tools redefine efficiency by automating the generation of register descriptions. High-level PSS descriptions seamlessly metamorphose into synthesizable RTL code, eliminating manual translation efforts and significantly reducing the likelihood of errors.

Integration with Verification: Reliability Reinforced

PSS seamlessly integrates with simulation and verification environments, empowering designers to validate their designs against specified properties and constraints. Incorporating PSS into the verification process enables early identification and resolution of potential CDC issues, reinforcing the overall reliability of the design.

PSS and UVM Harmony: Unifying Design and Verification

The seamless integration of PSS with the Universal Verification Methodology (UVM) propels the verification process to new heights. PSS descriptions effortlessly translate into UVM constructs, providing a harmonious transition from high-level design intent to comprehensive verification scenarios.

Case Study: PSS at the Helm of SoC Design Excellence

Consider a System-on-Chip (SoC) design with intricate clock domain structures. Through PSS, designers articulate synchronization requirements, ensuring a seamless data transfer symphony. The scenario modeling capabilities pinpoint potential metastability scenarios, empowering designers to implement targeted solutions proactively. The automatic generation of RTL code from PSS not only expedites the design flow but also forges a direct and harmonious path from high-level intent to implementation.

Conclusion: PSS - Elevating Design to a Symphony of Excellence

In conclusion, the fusion of the PSS data model and tools into the hardware design process signals a revolution, providing a comprehensive solution for the automatic handling of register clock domain crossings. PSS's expressive power, automated generation capabilities, and seamless integration with verification methodologies redefine design efficiency. As the intricate dance of hardware complexity continues, embracing technologies like PSS becomes imperative for designers aiming to lead the symphony of innovation with precision and confidence. PSS emerges not merely as a tool but as the orchestrator, guiding hardware design into a realm of unprecedented excellence.

0 notes

Text

Optimizing IP Integration: Harnessing the Power of SystemRDL to IP-XACT Conversion

In the dynamic landscape of electronic design, the seamless integration of Intellectual Property (IP) is paramount. This article explores the transformative power of converting SystemRDL to IP-XACT, elucidating how this process streamlines IP integration and enhances the efficiency of electronic system development.

Understanding SystemRDL and IP-XACT

SystemRDL (Register Description Language) and IP-XACT (IP eXchange and Configuration) are crucial elements in electronic design. SystemRDL provides a concise and powerful means of describing registers, while IP-XACT serves as a standardized format for IP metadata and configuration information.

The Integration Challenge

Integrating diverse IPs into a cohesive system poses challenges, often exacerbated by the heterogeneous formats in which IP information is presented. SystemRDL to IP-XACT conversion emerges as a solution, harmonizing disparate IP descriptions into a unified and interoperable format.

Streamlining IP Integration with SystemRDL to IP-XACT Conversion

1. Consistency in IP Descriptions:

Converting SystemRDL to IP-XACT ensures uniformity in IP descriptions. This consistency simplifies the integration process, reducing ambiguity and minimizing errors during IP assembly.

2. Enhanced Reusability:

IP-XACT promotes reusability by encapsulating IP information in a standardized manner. SystemRDL to IP-XACT conversion unlocks the potential for seamless reuse of IP across various projects and platforms.

3. Improved Interoperability:

The conversion process enhances interoperability by aligning diverse IPs under a common standard. This facilitates smoother communication between design and verification teams, fostering a collaborative and efficient development environment.

Tools Facilitating SystemRDL to IP-XACT Conversion

Several tools specialize in the conversion from SystemRDL to IP-XACT, automating the process and ensuring accuracy. These tools bridge the gap between different IP description languages, providing a cohesive framework for integration.

Realizing the Benefits in Practical Applications

Examining practical applications of SystemRDL to IP-XACT conversion unveils its impact on IP integration. Case studies demonstrate accelerated development cycles, reduced integration efforts, and enhanced project scalability.

Challenges and Considerations

While the conversion process brings substantial benefits, it is essential to acknowledge potential challenges. Addressing issues such as semantic differences between languages and tool compatibility ensures a smooth transition.

Conclusion: Unlocking Synergy in IP Integration

In conclusion, the conversion from SystemRDL to IP-XACT is a pivotal step towards unlocking synergy in IP integration. This process streamlines electronic system development, fostering consistency, reusability, and interoperability. Embracing the power of SystemRDL to IP-XACT conversion is not merely an optimization; it is a strategic move towards a future where IP integration is seamlessly efficient, setting new standards in electronic design.

0 notes

Text

Optimizing Verification Efficiency with PSS Compiler and UVM Testbench Integration

In the fast-paced realm of semiconductor design and verification, harnessing powerful tools and methodologies is crucial to ensure a smooth and efficient development process. Two key players in this domain are the Portable Stimulus Standard (PSS) and the Universal Verification Methodology (UVM). In this blog post, we'll delve into the integration of PSS Compiler and a UVM testbench, highlighting how this synergy can significantly enhance verification productivity.

Understanding PSS and its Role in Verification

The Portable Stimulus Standard (PSS) has emerged as a game-changer in verification methodologies. It provides a high-level representation of verification intent, enabling the creation of reusable test scenarios that can be easily retargeted across different verification platforms. PSS promotes a shift-left approach by allowing verification engineers to start the verification process much earlier in the design cycle.

By abstracting the test intent from the implementation details, PSS offers a concise and expressive way to describe complex scenarios, making it an invaluable tool for teams dealing with the intricacies of modern semiconductor designs. This standardization facilitates collaboration and improves overall efficiency in the verification process.

UVM Testbench and its Role in Functional Verification

Complementing PSS, the Universal Verification Methodology (UVM) has become the de facto standard for functional verification in the semiconductor industry. UVM provides a systematic approach to verifying complex designs by offering a standardized methodology, ensuring consistency across projects and facilitating code reuse.

A crucial component of UVM is the testbench, which is responsible for verifying the functionality of a design under various scenarios. The UVM testbench, with its modular structure, promotes scalability and maintainability, crucial factors in the verification of large and intricate designs.

Unlocking Synergy: PSS Compiler and UVM Testbench Integration

The integration of PSS Compiler with a UVM testbench brings about a paradigm shift in the verification landscape. This integration allows for a seamless transition of test intent from the abstract PSS representation to the detailed UVM testbench implementation.

With PSS Compiler, the high-level verification intent is captured concisely, reducing the effort required to create and maintain test scenarios. The compiler then generates the necessary UVM components, including sequences, drivers, and monitors, ensuring a direct mapping between the abstract PSS description and the UVM testbench.

This integration not only streamlines the verification process but also enhances collaboration among team members. The abstraction provided by PSS allows design and verification engineers to work concurrently on different aspects of the project, promoting a collaborative and efficient development environment.

UVM Register Model Example: Bringing it All Together

To illustrate the power of PSS Compiler and UVM testbench integration, let's consider the scenario of verifying a complex register model using the UVM methodology.

Assume we have a design with a sophisticated register structure, and we want to verify its functionality using a UVM testbench. PSS Compiler enables us to describe the register access sequences at a high level, specifying the desired register configurations and the corresponding expected behavior.

The compiler then translates this abstract description into UVM sequences, drivers, and monitors, seamlessly integrating them into the UVM testbench. This automation significantly reduces the time and effort traditionally required to manually create and maintain register access sequences in a UVM environment.

Agnisys: Empowering Seamless Integration

In this landscape of advanced verification methodologies, Agnisys stands out as a leader in providing tools that empower semiconductor design and verification teams. With Agnisys's commitment to innovation and efficiency, the integration of PSS Compiler and UVM testbench becomes not just a possibility but a practical and transformative reality.

By leveraging Agnisys's expertise, teams can navigate the complexities of semiconductor design and verification with confidence, knowing that they have robust tools at their disposal to optimize their workflows.

Conclusion

In the ever-evolving field of semiconductor design and verification, the integration of PSS Compiler and UVM testbench emerges as a powerful strategy to enhance efficiency and collaboration. This synergy, exemplified by the seamless integration of abstract verification intent with detailed testbench implementation, is pivotal in meeting the challenges posed by modern semiconductor designs.

Agnisys, with its commitment to advancing verification methodologies, plays a crucial role in empowering design and verification teams. The integration of PSS Compiler and UVM testbench not only aligns with industry best practices but also propels teams toward achieving new heights in verification efficiency and productivity.

0 notes

Text

IP-XACT: Revolutionizing Electronic System Design for a Connected World

In the ever-evolving landscape of electronics, where innovation is the driving force, there is a constant demand for more efficient, interconnected, and reliable electronic systems. IP-XACT, the Intellectual Property (IP) Extensible Markup Language (XML) Architecture and Process Automation Council, has emerged as a game-changer, revolutionizing electronic system design. This article delves deep into the transformative power of IP-XACT, its evolution, and its significance in shaping the connected world of the future.

IP-XACT: A Foundation for Collaboration

IP-XACT serves as the foundation for seamless collaboration in the complex world of electronic system design. It offers a standardized way to describe, package, and exchange IP components, making it easier for designers to work together. This standardization ensures that IP components from various sources can be seamlessly integrated, reducing errors and enhancing design consistency.

The Evolution of IP-XACT: From XML to 2022

The journey of IP-XACT began with the adoption of XML, which allowed for structured and extensible descriptions of IP components. Over the years, IP-XACT has evolved to keep pace with the growing demands of the industry. The 2022 version represents the latest iteration, offering significant enhancements:

Enhanced Metadata: IP-XACT 2022 provides an expanded set of metadata elements, offering more comprehensive descriptions of IP components. This facilitates precise design data exchange and minimizes interpretation errors.

Improved Configuration Management: Configuration management is crucial when dealing with various IP blocks. IP-XACT 2022 introduces enhanced support for configuration management, streamlining the design process.

Streamlined Debugging: Debugging and error-checking are made more accessible in the 2022 version. Designers can quickly identify and rectify issues, leading to faster development cycles.

Vendor-Neutrality: IP-XACT remains vendor-neutral, ensuring that designers can use different Electronic Design Automation (EDA) tools and IP components without compatibility issues.

The Role of IP-XACT Checker

IP-XACT Checker plays a pivotal role in the IP-XACT ecosystem by ensuring compliance with the IP-XACT standard. It acts as a vigilant guardian, meticulously validating descriptions to maintain the integrity of the design.

Functions of IP-XACT Checker:

Syntax Validation: It checks the syntax of IP-XACT descriptions, ensuring adherence to the standard. This includes verifying the presence of all required elements and correct XML formatting.

Semantics Verification: Beyond syntax, IP-XACT Checker validates the semantics of descriptions, ensuring that elements are used meaningfully and consistently.

Cross-Referencing: The tool verifies references within descriptions to ensure they point to the correct components, maintaining design integrity.

Consistency Checks: IP-XACT Checker ensures that descriptions are internally consistent, eliminating conflicts or contradictions.

IP-XACT Checker is the first line of defense against errors in the design process, promoting quality and consistency.

IP-XACT Integrator: The Glue for Complex Designs

IP-XACT Integrator simplifies the integration of IP blocks into complex electronic system designs. It acts as the bridge that connects various components, streamlining the integration process and making it more efficient.

Key Functions of IP-XACT Integrator:

IP Block Selection: Designers can select the most suitable IP blocks for their projects, evaluating compatibility and functionality.

Configuration Management: IP-XACT Integrator handles the configuration of IP blocks, ensuring accurate and consistent settings.

Connection Management: It oversees connections between IP blocks, including buses, signals, and interfaces, ensuring accuracy and preventing errors.

Simulation and Verification: The tool supports simulation and verification of the integrated design, identifying issues before implementation.

Documentation Generation: IP-XACT Integrator can generate documentation for the integrated design, enhancing understanding and maintenance.

The Future of IP-XACT in a Connected World

As the world becomes more connected, the demand for complex and reliable electronic systems continues to rise. IP-XACT, with its ever-evolving standards and robust ecosystem of tools, is set to play a central role in meeting these demands. It will continue to drive efficiency, reduce errors, and enhance collaboration in the electronic system design process.

Designers who embrace IP-XACT and its associated tools are better equipped to navigate the challenges of creating the next generation of electronic systems. The future holds promises of more interconnected, efficient, and reliable electronic systems, and IP-XACT will be at the forefront, shaping this connected world. It is not merely a tool or standard but a catalyst for innovation, enabling a future where electronic systems seamlessly connect us all.

0 notes

Text

Mastering Hardware Verification with UVM Testbenches, Register Models, and Sequences

Introduction:

In the world of hardware design and verification, ensuring the correctness and reliability of digital designs is paramount. The Universal Verification Methodology (UVM) has emerged as a powerful framework that simplifies and standardizes the verification process. In this technical article, we will delve into three crucial components of UVM verification: UVM Testbenches, UVM Register Models, and UVM Register Sequences. Together, these elements form a comprehensive approach to hardware verification that ensures the accuracy of digital designs.

UVM Testbench: The Backbone of Verification

The UVM Testbench serves as the cornerstone of the verification process. It is responsible for creating a controlled environment that mimics the operation of the actual hardware and enables the testing of various scenarios.

Key Aspects of UVM Testbenches:

Component-Based Architecture: UVM Testbenches are organized into modular components, each responsible for specific aspects of the verification process. This component-based architecture enhances reusability and maintainability.

Transaction-Level Modeling: UVM Testbenches use transaction-level modeling to simulate interactions between the testbench and the design under test (DUT). This approach allows for high-level, scenario-based testing.

Constrained Random Testing: UVM Testbenches employ constrained random testing, a powerful technique that generates a wide range of test cases based on specified constraints, enhancing test coverage.

Functional Coverage: UVM Testbenches incorporate functional coverage to track and report the progress of verification. This helps ensure that verification goals are met.

Interactions with UVM Register Models: The testbench interfaces with UVM Register Models to interact with and validate registers within the DUT. This collaboration ensures the verification of register functionality.

UVM Register Model Example: Abstract Representation of Registers

UVM Register Models provide an abstract representation of registers and memory-mapped structures within the DUT. They play a critical role in verifying register-based functionality.

Components of UVM Register Models:

Register Maps: UVM Register Models define register maps, which abstractly represent the complete set of registers and memory structures within the DUT. This organized structure simplifies the navigation and management of the verification environment.

Register Files: Registers are hierarchically organized into register files, mirroring the DUT's hierarchical structure. This organization is particularly beneficial for designs with complex hierarchical structures.

Automated Self-Checking: UVM Register Models simplify the generation of self-checking testbenches, reducing the manual effort required for creating robust and self-verifying test environments.

Coverage and Analysis: The integration of UVM Register Models facilitates comprehensive coverage collection and analysis, ensuring that verification engineers have the tools to thoroughly validate the design.

UVM Register Sequences: Controlled Register Interactions

UVM Register Sequences are designed to systematically interact with registers within the DUT. They ensure controlled and targeted access to registers, enhancing testbench modularity and reusability.

Key Features of UVM Register Sequences:

Sequence Abstraction: UVM Register Sequences provide an abstraction for generating sequences of register transactions, making it easy to create complex register interactions.

Scenario-Based Testing: Verification engineers can create scenario-specific sequences, tailoring interactions to different test scenarios, thus enhancing the versatility of the testbench.

Randomization and Constraint-Based Sequencing: Sequences can employ randomization and constraint-based techniques to generate various register transactions. This approach ensures comprehensive testing of registers.

Integration with UVM Register Models: UVM Register Sequences interface with UVM Register Models to ensure that the generated sequences accurately reflect the behavior of registers in the DUT.

A Holistic Approach to Hardware Verification

The synergy between UVM Testbenches, UVM Register Models, and UVM Register Sequences offers a holistic approach to hardware verification. By combining these elements, verification engineers can thoroughly test and validate the functionality of digital designs, ensuring that they meet the highest standards of accuracy and reliability.

Benefits of This Approach:

Modularity and Reusability: The component-based architecture of UVM Testbenches, abstract representation in UVM Register Models, and scenario-based testing with UVM Register Sequences enhance modularity and reusability in the verification process.

Coverage and Traceability: Functional coverage and traceability are integrated into the UVM framework, ensuring that verification engineers can measure progress and meet verification goals effectively.

Accurate Register Verification: The collaboration between UVM Testbenches and UVM Register Models ensures that registers within the DUT are accurately and thoroughly verified, reducing the risk of functional errors.

Scenario-Specific Testing: UVM Register Sequences enable scenario-specific testing, ensuring that digital designs are rigorously tested in various real-world scenarios.

Conclusion:

UVM Testbench, UVM Register Models, and UVM Register Sequences form a comprehensive approach to hardware verification. These elements, when integrated and utilized effectively, provide verification engineers with the tools and methodologies necessary to ensure the accuracy and reliability of digital designs. This holistic approach simplifies the verification process and facilitates the achievement of the highest standards in hardware verification.

0 notes

Text

Mastering Clock Domain Crossing: A Deep Dive into Register Design

Introduction: Clock Domain Crossing (CDC) is a crucial aspect of digital design that plays a pivotal role in modern electronic systems. Ensuring a robust and reliable CDC process is essential for maintaining the integrity of your digital signals. In this technical blog, we will delve into the intricacies of CDC and explore the fundamentals of register design to tackle this challenging aspect of digital design.

Understanding Clock Domain Crossing (CDC):

Clock domains are distinct regions of a digital circuit that are governed by separate clock signals. When data crosses from one clock domain to another, synchronization issues can arise, leading to potential data corruption and system failures. This is where CDC comes into play, as it manages data transfers between these clock domains.

Synchronization Elements: Synchronization elements, such as flip-flops, are key components used in CDC. They act as bridges between different clock domains, ensuring that data transfers occur in a controlled and synchronized manner.

Metastability: Metastability is a significant concern in CDC. When data transitions between domains, it can briefly enter an uncertain state, causing unpredictable results. Proper register design and synchronization techniques are crucial in minimizing metastability.

Register Design for CDC:

Effective register design is critical to ensuring the reliability of CDC. Here are some key considerations:

Gray Code Encoders: Gray code encoders are used to encode binary signals into Gray code, which has only one-bit change at a time. This reduces the chances of metastability during data transfer.

Two-Flip-Flop Synchronizers: Using a two-flip-flop synchronizer can significantly reduce the metastability window. Data is latched by the first flip-flop and then transferred to the second, ensuring that only stable data passes through.

Proper Timing Constraints: Defining accurate timing constraints is essential in CDC. This includes setup and hold times for data signals to guarantee that data is captured correctly in the receiving clock domain.

Asynchronous FIFOs: Asynchronous First-In-First-Out (FIFO) buffers can be employed to safely transfer data between clock domains. They manage data transfer, handle data width differences, and maintain a synchronized interface.

Challenges and Solutions:

Clock Domain Asymmetry: When clock domains have different frequencies, ensuring reliable CDC becomes more challenging. Careful synchronization and data transfer techniques are needed to address this issue.

Data Width Mismatch: When data buses have different widths in source and destination domains, appropriate data padding or extraction mechanisms should be implemented.

Conclusion:

Clock Domain Crossing is a complex yet critical aspect of digital design. By understanding the fundamentals of CDC and implementing effective register design techniques, you can ensure that your digital systems work reliably and consistently. Proper synchronization elements and careful consideration of timing constraints are key to mastering CDC and preventing data corruption.

In the world of digital design, CDC is a fundamental challenge that, when tackled effectively, can lead to robust and dependable electronic systems.

0 notes

Text

Simplifying UVM Model Generation with the Register Model Generator

In the realm of digital design and verification, the Universal Verification Methodology (UVM) has established itself as the gold standard for developing and verifying complex hardware designs. UVM provides a systematic and standardized way to verify digital designs, making it an invaluable tool in the semiconductor industry. One crucial aspect of UVM is the generation of UVM models, particularly register models, which are essential for the verification process. In this blog post, we will demystify the process of UVM model generation, with a focus on the Register Model Generator.

What is UVM Model Generation?

UVM model generation is the process of creating UVM-compliant models that represent the functionality of a hardware design. These models serve as the interface between the verification environment and the design under test (DUT). Register models, in particular, define the registers within a design and their behavior, allowing for seamless interaction and validation of the DUT.

The Role of Register Models

Register models play a pivotal role in the verification process. They provide a virtual representation of the registers in the design, allowing verification engineers to read and write to these registers, mimic real-world scenarios, and ensure the DUT behaves as expected. This level of abstraction is essential for testing the design thoroughly.

Introducing the Register Model Generator

Creating UVM register models manually can be a daunting and time-consuming task. This is where the Register Model Generator comes into play. It is a powerful tool that simplifies and automates the process of generating UVM register models. Let's explore some of its key features and advantages:

Efficiency: The Register Model Generator significantly reduces the time and effort required to create register models. It takes a register description and automatically generates the necessary UVM code, saving valuable resources.

Consistency: Manual model creation can lead to inconsistencies and errors. The generator ensures that the generated models are consistent and adhere to UVM guidelines.

Customization: While automation is a significant advantage, the Register Model Generator also allows for customization. Engineers can fine-tune the generated code to meet specific project requirements.

Ease of Use: The tool is designed to be user-friendly, making it accessible to both novice and experienced verification engineers.

Integration: It seamlessly integrates with UVM verification environments, making it a versatile choice for different projects.

The Workflow with the Register Model Generator

Input Register Description: Start by providing a register description of the DUT. This typically includes details such as register addresses, bitfields, access types, and register properties.

Generate UVM Code: The Register Model Generator processes the input description and generates UVM-compliant register models.

Customization (if needed): Engineers can review and customize the generated code to match project-specific requirements.

Integration: Integrate the generated models into the UVM verification environment, enabling comprehensive testing of the DUT.

Conclusion

UVM model generation, especially register model creation, is a critical step in the verification of digital designs. The Register Model Generator streamlines this process, making it more efficient and reliable. By automating the generation of UVM-compliant register models, engineers can focus on what truly matters – comprehensive design verification. In a field where time-to-market is crucial, tools like the Register Model Generator are invaluable, ensuring that hardware designs meet the highest standards of quality and functionality. So, if you are involved in digital design and verification, consider simplifying your UVM model generation process with this powerful tool.

0 notes

Text

Empowering Embedded Engineers: The Unseen Magic of PSS Compilers

In the world of embedded systems, where precision and efficiency reign supreme, engineers and designers are continually seeking innovative solutions to streamline their development processes. One such solution that often goes unnoticed is the Power System Simulation (PSS) compiler—a powerful tool that silently but significantly enhances the capabilities of embedded engineers. In this article, we will delve into the realm of PSS compilers and explore how they assist embedded engineers and designers in their quest for excellence.

Understanding PSS:

Before we dive into the benefits of a PSS compiler, let's establish a clear understanding of what PSS is. Power System Simulation, or PSS, is a modeling approach that allows engineers to simulate, analyze, and optimize the power systems within embedded devices. It provides an invaluable representation of how power flows within a system, enabling engineers to make informed decisions and improvements.

The PSS Compiler: A Catalyst for Success:

Now, let's turn our attention to the unsung hero in this narrative—the PSS compiler. A PSS compiler is a software tool that translates a PSS model into executable code for a target hardware platform. It takes the intricate power system simulations and transforms them into tangible, real-world applications.

Here's how a PSS compiler can help embedded engineers and designers:

Efficient Development: PSS compilers simplify the process of converting complex power system simulations into code. This streamlines development, saving engineers time and effort that can be redirected towards improving other aspects of the system.

Optimized Power Management: With a PSS compiler, engineers can fine-tune power management within their embedded systems. This means better energy efficiency, longer battery life, and reduced power-related issues.

Rapid Prototyping: PSS compilers facilitate rapid prototyping, allowing engineers to test different power system configurations quickly. This accelerates the development cycle and aids in identifying the most efficient solution.

Reduced Errors: By automating the translation of PSS models into code, PSS compilers significantly reduce the risk of human error. This results in more reliable and robust embedded systems.

Cross-Platform Compatibility: PSS compilers often support multiple hardware platforms, making it easier for engineers to adapt their designs to different target systems without extensive manual adjustments.

The Power of PSS Models:

PSS models are at the core of this process. They serve as the foundation upon which a PSS compiler operates. These models define the behavior of a power system under various conditions, allowing engineers to conduct simulations and evaluate performance.

Creating an accurate and comprehensive PSS model is a crucial step. It requires a deep understanding of the power requirements, components, and interactions within the embedded system. However, the benefits of investing time in constructing a solid PSS model are well worth it in terms of reduced development time and superior system performance.

Selecting the Right PSS Tool:

To fully harness the potential of PSS compilers, embedded engineers and designers must choose the right PSS tool for their specific needs. There are various tools available, each with its own set of features and capabilities. Factors such as compatibility, ease of use, and support for target platforms should guide this decision.

In conclusion, the world of embedded engineering is a complex and dynamic field. PSS compilers play a critical role in simplifying this complexity, allowing engineers and designers to create more efficient and reliable systems. By embracing the power of PSS models and selecting the right PSS tool, embedded professionals can unlock the full potential of their designs, ensuring that their creations are not just functional but also energy-efficient and future-ready.

0 notes

Text

How is a Portable Stimulus Standard helpful?

The Portable Test and Stimulus Standard (PSS) establishes a specification for creating a unified representation of stimulus and test scenarios. This representation is designed to be accessible to a wide range of users, accommodating different levels of integration and various configurations. It empowers the generation of diverse implementations of a scenario that can run on various execution platforms, including simulation, emulation, FPGA prototyping, and post-silicon testing. With this standard in place, users can define a set of behaviors once, which can then serve as the basis for deriving multiple implementations. Any SOC design team wishing to streamline their register integration procedure must have the Agnisys PSS Compiler. This robust compiler transforms register descriptions published in UVM and C/C++ headers to various formats, including SystemRDL and IP-XACT. Teams can speed up the verification closing process and avoid labor-intensive manual coding with the feature-rich Agnisys PSS tool suite.

0 notes

Text

Cultivating High-Quality IP-XACT Compliant UVM Register Models

In today's fast-evolving semiconductor industry, the requirement for solid and interoperable solutions has never been more significant. UVM (Universal Verification Methodology) register model generation is a crucial component of semiconductor design. For planning, verifying, and validating intricate hardware designs, these models are crucial. It is essential to develop top-notch UVM register models that adhere to IP-XACT standards in order to guarantee easy integration and interoperability. The importance of IP XACT quality in UVM register model and how it supports effective semiconductor design will be discussed in this article.

What is UVM Regmodel?

An abstract SystemVerilog model called UVM_REG represents the DUT's registers and memories. It was constructed utilizing UVM principles. The UVM Regmodel is presented in detail here.

What is IP-XACT?

An XML Schema for meta-data documenting Intellectual Property (IP) used in the development, implementation, and verification of electronic systems is described in IEEE 1685, "Standard for IP-XACT, Standard Structure for Packaging, Integrating, and Re-Using IP Within Tool-Flows," along with an Application Programming Interface (API) to give tools access to the meta-data.

UVM Register Models Overview

Let's first define UVM register models and their function in semiconductor design before going into the significance of IP-XACT quality in UVM register models.

The Universal Verification Methodology (UVM), a widely used methodology for evaluating integrated circuits, which includes UVM register models as a crucial part. These models explain how registers behave and have specific properties inside a hardware design, such as their fields, access rules, reset values, and more. Engineers are able to precisely simulate, test, and verify the functioning of a hardware design thanks to UVM register models, which act as a link between the design and verification environments.How High-quality

UVM Register Models Are Important?

It is essential to produce high-quality UVM register models for the following reasons:

Accuracy: The registers in the hardware design are faithfully modeled by high-quality UVM register models. Any inconsistencies or faults in the models could result in design mistakes that wouldn't be discovered until later stages of development, costing money in modifications.

UVM register models should effortlessly connect with a variety of verification and design tools to ensure interoperability. To avoid compatibility problems and speed up the design and verification process, it is crucial to ensure compatibility and adherence to industry standards.

Reusability: Well-designed UVM register models can be used by numerous teams and projects. By removing the need to construct new models for similar ideas, this reusability shortens development cycles and saves time and labor.

Maintainability: UVM register models must stay current as hardware designs change and are updated. It is simpler to maintain high-quality models, ensuring that they precisely reflect the current design and lowering the possibility of mistakes brought on by out-of-date models.

Wholly Integrated Solutions for the IC Development Process

Every team on your SoC or IP project will profit from the specification automation tools offered by the Agnisys IDesignSpec Suite of products. Automatic file generation from executable specifications is used by designers, verification engineers, embedded programmers, pre-silicon validation engineers, and the post-silicon lab bring-up team. Technical writers can utilize the documentation in these files directly in user manuals.

Throughout your project, the Agnisys solution is advantageous to all teams. Hand coding is replaced by the automatic generation of every file. Each updated file produced when the standard changes eliminates the need for manual updating. Every stage on your project timeline occurs early and uses a lot less priceless labor.

Products that Streamline the Development of Semiconductors

Your product teams can access a connected set of products through the Agnisys product suite, comprising a unified graphical design interface (GDI) front end and a united generation engine. In order to maximize productivity and support completely automated flows, these can be shared throughout all of your teams.

IDesignSpec GDI

IDS-Batch CLI

IDS-Verify

IDS-Validate

IDS-Integrate

IDS-IPGen

Exceptional Customer Service

High client satisfaction and timely customer service are among Agnisys' core principles. In order to respond quickly, our application engineers are situated close to where our users are. Users of our client portal have access to the most recent:

Downloads of programs

Announcements about products

Courses in product and technology

Configuring licenses and requesting temporary licenses

Issues with Agnisys' issue tracking system that are particular to customers

Newsletter, Blogs and Webinars

Trainings on various technologies

Modern semiconductor design requires the development of high-quality IP-XACT-compliant UVM register models. These models are essential for testing hardware designs and making sure they work with different EDA tools and design environments. Design teams can improve the precision, reusability, maintainability, and long-term viability of their UVM register models by following IP-XACT standards, which will ultimately result in more effective and affordable semiconductor design procedures.

Agnisys is dedicated to providing cutting-edge solutions that enable semiconductor designers to fulfill the highest standards of quality and interoperability. We understand the importance of IP-XACT quality in UVM register models. We offer the knowledge and resources to meet your requirements whether you're looking to develop, test, or integrate UVM register models that are IP-XACT compatible. For more information on how we can assist you with developing superior IP-XACT-compliant UVM register models for your semiconductor design projects, get in touch with us right away.

0 notes

Text

How can a PSS compiler help embedded engineers and designers?

For semiconductor design and verification, Agnisys provides leading-edge PSS tools and compilers. To speed up the SOC integration process for embedded engineers and designers, the Agnisys PSS compiler automates challenging register and sequence conversions. The verification closure is accelerated by the Agnisys PSS tools ecosystem’s powerful capabilities, such as Verification & Validation models and environment PSS tools generate outputs such as automated tests to accelerate verification closure.

With Agnisys PSS Compiler (APC) the inputs from Register/Memory specification and the sequence specification are generated as outputs:

Models: RTL,UVM RAL, C/C++ headers,documentation (HTML,PDF)

Run Env.: Verification (SV/UVM) , Validation (C/C++)

Tests: Automatic tests (UVM and C/C++), PSS based custom tests (UVM and C/C++)

Misc. : Custom outputs (Velocity template), Makefile, main.c

0 notes

Text

Unlocking Efficiency and Interoperability: The Benefits of IP-XACT

Engineers and designers continually seek ways to streamline their workflows and improve collaboration in the ever-evolving world of electronic design, where complexity and innovation are paramount. IP-XACT (IP eXtensible Markup Language - XML for Intellectual Property) is a robust standard that has gained prominence in electronic design automation. This blog post will delve into IP-XACT, its advantages, and how it unlocks efficiency and interoperability in electronic design.

What is IP-XACT?

IP-XACT is an open, XML-based standard developed to enable semiconductor intellectual property (IP) descriptions and design data interoperability and reusability. This standard provides a common language and framework for describing and packaging electronic design information, making it easier for different electronic design automation.

What are the advantages of IP-XACT?

Streamlined Collaboration - Collaboration between teams and organizations is made more straightforward with IP-XACT. Design data and IP components are described in a standardized format, eliminating the need for manual translation or adaptation. It fosters better communication and cooperation among design teams.

Improved Documentation - Accurate and up-to-date documentation is crucial in electronic design. IP-XACT provides a standardized way to document IP components, making it easier for designers to understand and work with them. This documentation also aids in IP compliance and quality assurance.

Efficiency in Design and Verification - IP-XACT simplifies integrating IP blocks into a larger design. Designers can quickly understand the functionality and interfaces of IP components, speeding up the design phase. Furthermore, the standardized structure and attributes aid in automating verification, reducing the likelihood of errors.

Tool Interoperability - IP-XACT encourages EDA tool vendors to support the standard, ensuring interoperability between different tools. Designers can choose the best-in-class tools for their specific tasks, knowing they will work together seamlessly through IP-XACT.

Easier IP Management - With IP-XACT, organizations can establish a centralized repository of IP components, making managing and tracking IP assets simple. This centralized approach improves version control and ensures that the most current IP components are used in designs.

Enhanced Reusability - One of the primary goals of IP-XACT is to promote IP reusability. Engineers can create, package, and document IP components once and then reuse them across multiple projects or within different teams. IP-XACT saves time, ensures consistency, and reduces the chances of errors during reuse.

Overall, without IP-XACT, the integration of these IP blocks could be a time-consuming and error-prone process. Engineers might need to manually decipher the specifications of each IP block and adapt them to fit into the larger design. Without IP-XACT, it increases the risk of mistakes and hampers collaboration between teams responsible for each IP block.

Final Thought -

In the dynamic world of electronic design, where innovation is relentless, and collaboration is essential, IP-XACT emerges as a critical enabler of efficiency and interoperability. Its ability to standardize IP descriptions, streamline design integration, and promote reusability makes it an asset for engineers and design teams. The benefits are clear: reduced development time, fewer errors, and a more robust foundation for innovation in the ever-advancing field of electronic design. Embrace IP-XACT and propel your creations into the future with confidence and agility. By adopting IP-XACT in your electronic design workflow, you unlock the potential for enhanced efficiency, improved collaboration, and seamless integration with diverse tools.

1 note

·

View note