Silicon and VLSI Engineering - Specification to Silicon Tapeout Insights

Don't wanna be here? Send us removal request.

Link

Looking at the criticality of DFM, it has become an important ingredient of product success. Here in this blog author have tried to include top 10 contributing factors to DFM.

3 notes

·

View notes

Link

Is Custom ASIC Revolutionize is your Next-Gen IoT Device?

0 notes

Link

Find out how 3DIcs are becoming key element across different Consumer electronics, AI and ML for their seamless performance in lower technology node design.

0 notes

Link

The key milestone in developing ASIC is taping it out on right time. In this blog, we will discuss several challenges and solutions that can be used to signoff the design like: Timing closure, pdv closure techniques, RPCT, and packaging complexity.

0 notes

Link

A promising solution : Memory BIST (Built-in Self-test), BIRA and BISR which adds test and repair circuitry to the memory and provides an acceptable yield. In the coming years, Moore’s law will be driven by memory technologies that focus on aggressive pitch scaling and higher transistor count.

0 notes

Link

Assertion is a very powerful feature of System Verilog HVL (Hardware Verification Language). Nowadays it is widely adopted and used in most of the design verification projects.

0 notes

Link

Looking at the criticality of DFM, it has become an important ingredient of product success. Here in this blog author have tried to include top 10 contributing factors to DFM.

0 notes

Video

tumblr

Watch this 1-minute video of eInfochips success story about #7nm lower #technology node design and #verification expertise. Are you also looking for end-to-end silicon #turnkey design services and support? Contact now: https://hubs.ly/H0r65wD0 #hyperscale #Datacenters

0 notes

Link

Major Complexities in IoT Design are:

IoT Device Data volume checks at less interval of time: Each IoT device has its own hardware and may have different variants of software. It becomes difficult to test all the possible combinations of huge number of data volume under less test time at a low cost.

IoT Device Faulty Behavior in deployment:....

0 notes

Text

Top 10 Contributing Factors to Design-for-Manufacturability (DFM)

Manufacturing is one of the key factors which determines product success, as it directly refers to product quality and availability. Design for Manufacturability (DFM) determines the process of ensuring optimum production efficiency and quality while taking care of potential product problems in the design phase itself.

DFM saves on time; costs and effort related to product redesigning process and carves out best-manufacturing output efficiently. It takes care of factors that might impact product manufacturing including the nature of raw material, its physical and chemical attributes and its availability for faster production.

Depending upon the industry and type of manufacturing process the DFM practices vary and are tamed to define checklists for quality and design checks. It has been estimated that by the time product design gets determined, about 80% (shown in the graph in Figure 1) of the total product costs are incurred. These designs determine the manufacturability which in turn impacts production costs. DFM has a vital role to play in controlling product costs.

Looking at the criticality of DFM, it has become an important ingredient of product success. Here in this blog, the author tried to include the top 10 contributing factors to DFM. to be continued...

#design for manufacturability#dft#dfm#semiconductor#technology#physical design services#chip design#microchip#supplychain costmodeling engineerteam designprocess

1 note

·

View note

Photo

This infographic defines the roadmap of eInfochips towards lower technology nodes migration from 180nm to 7nm to power multiple applications in datacenter chips, networking, artificial intelligence, machine learning, etc.

2 notes

·

View notes

Link

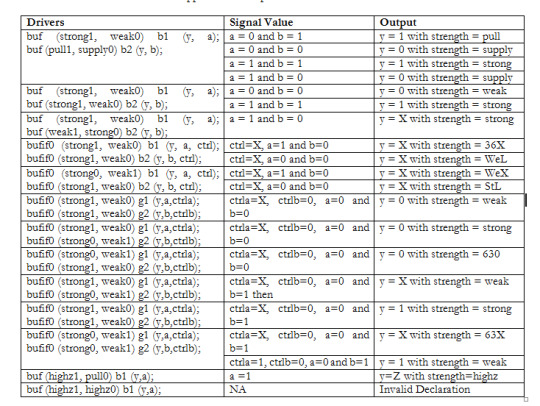

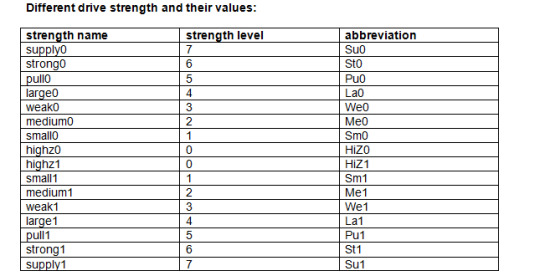

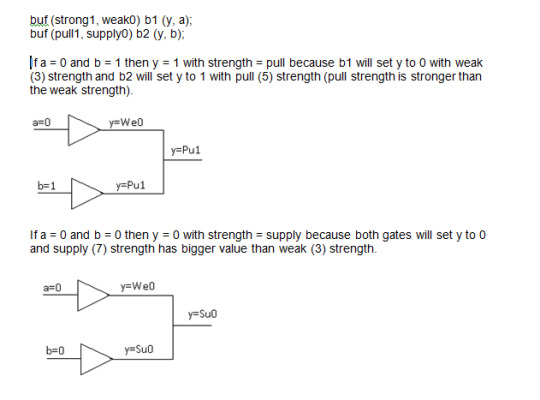

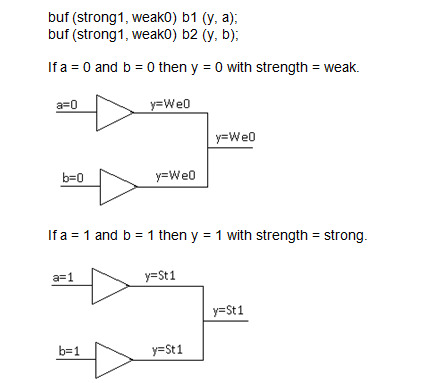

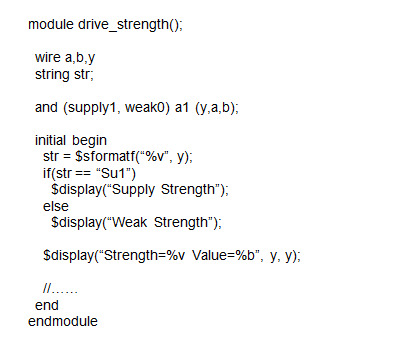

In this blog, eInfochips showcase how signal drive strength can be checked in SystemVerilog for best possible results, and the various rules which have to be observed in “documenting” signal strength.

1 note

·

View note

Photo

(via How to Check Signal Drive Strength in SystemVerilog)

0 notes

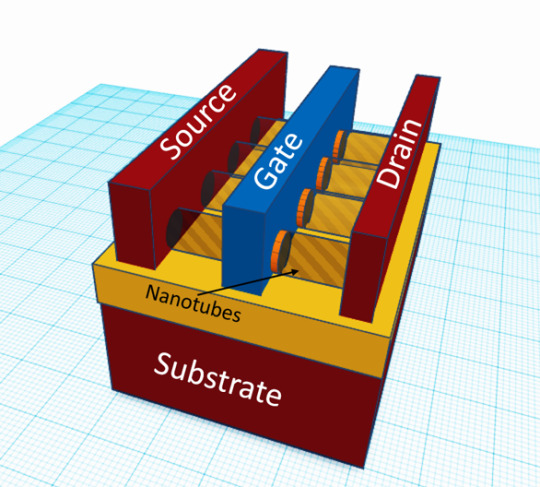

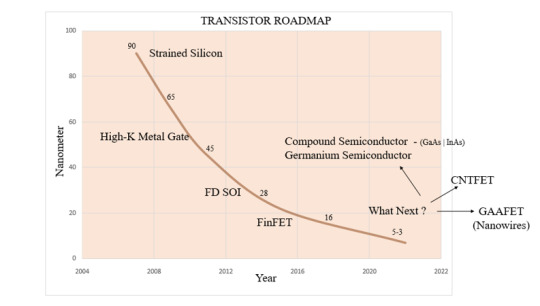

Photo

(via Overcoming challenges of futuristic transistor technology below 5nm node)

1 note

·

View note