#RISCV

Explore tagged Tumblr posts

Text

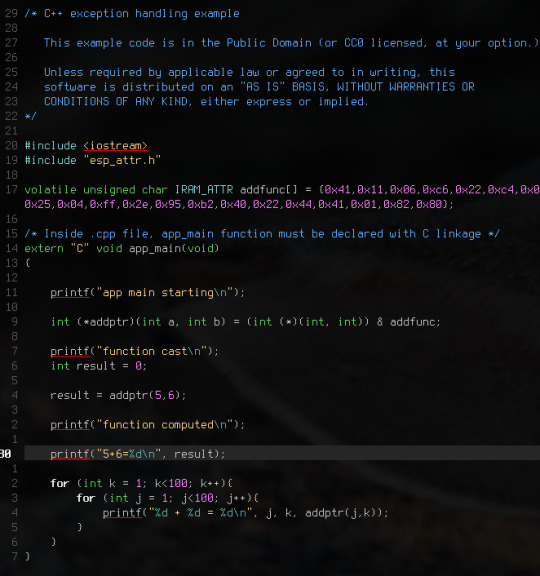

(doing something stupid) can you allocate an array at a specific address during compile time in C++. This system is Harva-actually wait the docs say this is almost a built in feature. Hang on.

Hell yes okay I have the thing I want working, you just have to. turn off memory protection and use the IRAM_ATTR thing. That's fine. I think I can make this work I'll just block out a couple kB of nops for my plugins. For a moment there I thought I was going to end up using WASM. I might still, WASM is infinitely safer than this. But this is very funny.

Love function pointer syntax. Makes perfect sense in that awful C way.

That array is just the -O0 implementation of an add in rv32. If you optimize it it's like two instructions but I just wanted to make sure I could execute more than one in a row. I think if you compile right with -fPIC/-fPIE and all that jazz you should just be able to dump that into RAM and execute. Since all your jumps will be relative?

22 notes

·

View notes

Text

youtube

Desk of Ladyada - It's a RISC-V kinda weekend https://youtu.be/aC3vGKHRCBA

MMade progress on two RISC-V projects to finalize PCBs. We optimized the CH32v203g6 chip-based QT Py board by reducing it from a 4-layer to a 2-layer to cut costs, and integrated TinyUSB support for better Arduino IDE compatibility. We also advanced the Feather ESP32-C6 project, enhancing its deep sleep power efficiency and finalizing the USB Key 'Trinkey' for standalone gateways or sensors. Plus, we picked out a clear USB enclosure from Digi-Key for it.

9 notes

·

View notes

Text

Starting Production🎉🥂

ZippOS is an alternate operating system for stand alone “spacial computing” devices. The goal of this project is to provide end users, who at their own discression, void their warranties to replace pre-packaged software bundled with their hardware. As the lead developer of ZippOS, and as an end user of a “spacial computer”, I am displeased with the current operating software, and the decisions of parent companies that distribute these products are inheriently unstable, brown-nosing share holders and consumers, and completely unaligned with the end users. As these devices are marketed as computers, I want to provide software for said computers as a choice for the end-users who feel the same as I do.

ZippOS will be a lighter(get it?), faster booting operating system built from scratch with Rust-Lang and some ARM/RISC-V assembly code to replace both the BIOS (ZIOS) and the operating system. The operating system’s goal is to have the same user functionality and multimedia multi-instancing in a mixed reality setting, citing BeOS/HaikuOS as inspiration. This operating system will have security and graceful degradation as the main focus for user safety because the main enemy for ZippOS is the companies who made the stock software it replaces on the end-user’s spacial computer. Users can also enjoy various stimulating options for navigating the software (i.e. “rolodex” style hub menus, table-top program/application storefront, “grabbing” and “throwing” programs/screens to be cast/mirrored to and from realspace and cyberspace, etc). ZippOS is a project software operating system under development, and currently has no plans to publicly publish to the open net, nor are there any current plans to open-source the software.

#ZippOS#Zipp-OS#Zipp OS#rustlang#rust-lang#operatingsystem#OS#linux#assembly language#assembly programming#riscv#arm64#mixed reality#virtual reality

8 notes

·

View notes

Text

OneAPI Construction Kit For Intel RISC V Processor Interface

With the oneAPI Construction Kit, you may integrate the oneAPI Ecosystem into your Intel RISC V Processor.

Intel RISC-V

Recently, Codeplay, an Intel business, revealed that their oneAPI Construction Kit supports RISC-V. Rapidly expanding, Intel RISC V is an open standard instruction set architecture (ISA) available under royalty-free open-source licenses for processors of all kinds.

Through direct programming in C++ with SYCL, along with a set of libraries aimed at common functions like math, threading, and neural networks, and a hardware abstraction layer that allows programming in one language to target different devices, the oneAPI programming model enables a single codebase to be deployed across multiple computing architectures including CPUs, GPUs, FPGAs, and other accelerators.

In order to promote open source cooperation and the creation of a cohesive, cross-architecture programming paradigm free from proprietary software lock-in, the oneAPI standard is now overseen by the UXL Foundation.

A framework that may be used to expand the oneAPI ecosystem to bespoke AI and HPC architectures is Codeplay’s oneAPI Construction Kit. For both native on-host and cross-compilation, the most recent 4.0 version brings RISC-V native host for the first time.

Because of this capability, programs may be executed on a CPU and benefit from the acceleration that SYCL offers via data parallelism. With the oneAPI Construction Kit, Intel RISC V processor designers can now effortlessly connect SYCL and the oneAPI ecosystem with their hardware, marking a key step toward realizing the goal of a completely open hardware and software stack. It is completely free to use and open-source.

OneAPI Construction Kit

Your processor has access to an open environment with the oneAPI Construction Kit. It is a framework that opens up SYCL and other open standards to hardware platforms, and it can be used to expand the oneAPI ecosystem to include unique AI and HPC architectures.

Give Developers Access to a Dynamic, Open-Ecosystem

With the oneAPI Construction Kit, new and customized accelerators may benefit from the oneAPI ecosystem and an abundance of SYCL libraries. Contributors from many sectors of the industry support and maintain this open environment, so you may build with the knowledge that features and libraries will be preserved. Additionally, it frees up developers’ time to innovate more quickly by reducing the amount of time spent rewriting code and managing disparate codebases.

The oneAPI Construction Kit is useful for anybody who designs hardware. To get you started, the Kit includes a reference implementation for Intel RISC V vector processors, although it is not confined to RISC-V and may be modified for a variety of processors.

Codeplay Enhances the oneAPI Construction Kit with RISC-V Support

The rapidly expanding open standard instruction set architecture (ISA) known as RISC-V is compatible with all sorts of processors, including accelerators and CPUs. Axelera, Codasip, and others make Intel RISC V processors for a variety of applications. RISC-V-powered microprocessors are also being developed by the EU as part of the European Processor Initiative.

At Codeplay, has been long been pioneers in open ecosystems, and as a part of RISC-V International, its’ve worked on the project for a number of years, leading working groups that have helped to shape the standard. Nous realize that building a genuinely open environment starts with open, standards-based hardware. But in order to do that, must also need open hardware, open software, and open source from top to bottom.

This is where oneAPI and SYCL come in, offering an ecosystem of open-source, standards-based software libraries for applications of various kinds, such oneMKL or oneDNN, combined with a well-developed programming architecture. Both SYCL and oneAPI are heterogeneous, which means that you may create code once and use it on any GPU AMD, Intel, NVIDIA, or, as of late, RISC-V without being restricted by the manufacturer.

Intel initially implemented RISC-V native host for both native on-host and cross-compilation with the most recent 4.0 version of the oneAPI Construction Kit. Because of this capability, programs may be executed on a CPU and benefit from the acceleration that SYCL offers via data parallelism. With the oneAPI Construction Kit, Intel RISC V processor designers can now effortlessly connect SYCL and the oneAPI ecosystem with their hardware, marking a major step toward realizing the vision of a completely open hardware and software stack.

Read more on govindhtech.com

#OneAPIConstructionKit#IntelRISCV#SYCL#FPGA#IntelRISCVProcessorInterface#oneAPI#RISCV#oneDNN#oneMKL#RISCVSupport#OpenEcosystem#technology#technews#news#govindhtech

2 notes

·

View notes

Text

FET113i-S SoM Now Supports RISC-V, Offering a Superior Cost-Effective Solution

FET113i-S is an industrial-grade SoM designed by Forlinx Embedded based on Allwinner T113-i processor. With excellent stability and ultra-high cost performance, FET113i-S SoM has gained wide attention from customers. As a multi-core heterogeneous architecture chip with an A7 core, a RISC-V core, and a DSP core, Allwinner Technology recently released the RISC-V core (XuanTie C906) details for the T113-i, and Forlinx embedded quickly adapted to this development.

1. What is RISC-V?

RISC-V is an open-source instruction set architecture (ISA) based on the principles of Reduced Instruction Set Computing (RISC). It was first introduced by the University of California, Berkeley in 2010 and has since gained significant attention and support from academia and industry worldwide. RISC-V architecture, characterized by its openness, simplicity, and scalability, is emerging as a formidable force in the global semiconductor industry.

2. What Are the Advantages of the T113-i's Risc-v?

High Efficiency and Low Power Consumption

RISC-V architecture follows the principles of reduced instruction set computer, which simplifies the hardware design, improves the execution efficiency and reduces the development cost. The RISC-V cores in the T113-i processor can efficiently perform a wide range of computational tasks while maintaining low power consumption, making it ideal for resource-constrained edge computing environments.

Modularity and Scalability

RISC-V architecture is designed with simplicity and modularity in mind, allowing different instruction set extensions to be chosen based on requirements. RISC-V core in the T113-i processor supports multiple standardized extension instruction sets, such as M (integer multiplication and division), A (atomic operations), and F/D/Q (single/double/quad-precision floating-point operations), enabling flexible combination and addition according to specific application scenarios.

Open Standard and No Licensing Fees

RISC-V is open source, allowing anyone to use and extend it for free, without licensing fees. This greatly promotes technology sharing and innovation, reducing product development costs.

Real-Time Performance

In the T113-i, the A7 core, RISC-V core, and DSP core can run simultaneously, realizing multi-core heterogeneous computing. This design enhances overall system performance and meets diverse application requirements. The RISC-V core, in particular, can accommodate applications with high real-time requirements, ensuring rapid response and processing of real-time data.

3. A Quality Choice for Cost Reduction

Forlinx Embedded FET113i-S SoM, with completed RISC-V core adaptation, is highly competitive in price. Its industrial-grade quality enables it to handle more complex application scenarios, while its comprehensive peripheral interface resources make it both powerful and user-friendly.

FET113i-S SoM's clear advantages, combined with Folinx Embedded's stable supply chain and robust technical support, ensure swift project implementation and market primacy for customers.

Originally published at www.forlinx.net.

0 notes

Text

youtube

0 notes

Text

They aren't just making their own phones: they're making their own ISAs (Loongarch, which is kind of a MIPS/RISCV mixture at this point), are heavily invested in RISCV as well, and are rapidly closing in on fabbing their own silicon that is on par with what comes out of the west.

The funny thing to me about American Liberal, specifically the Democratic party, fearmongering about China in 2024 is that we have so much more immediate issues to deal with. Like objectively.

We have Climate Change and mass failing infrastructure to deal with (A Green new deal could of addressed it, the Democratic party scared of Republican attacks buried it)

We have cops who will murder you or your dog, cry about it on the news and get a promotion and months of paid vacation (Defunding the police could of addressed it, the Democratic party scared of Republican attacks buried it)

We have massive wealth inequality and class disparity that Nazi Collaborator Elon Musk was able to buy his way into Power (Taxing the Rich at levels Pre Ronald Reagan could address it, the Democratic party scared of Republican attacks buried it. Also Obama basically enabled this with his response to the 2008 financial crisis but that’s a longer discussion)

We have student debt and medical debt crippling young people in this country (Getting Rid of it could have addressed it, the Democratic party scared of Republican attacks buried it after several half measures by Biden)

There’s also the fascism at home and the imperial expansion and genocide draining resources and so much more but you get the point. China ain’t going to destroy Us, we are already past halfway there. Leftist policies actually could have addressed this issue but Liberals wanted to be bffs with the American Fascist movement.

#politics#tariffs#capitalism#socialism#china#cpc#xi jinping#comrade xi#tech#riscv#loongarch#electrical engineering#computer engineering#chipfab#chip fab

214 notes

·

View notes

Text

okay if there are jumps something goes screwy. At present I am literally just copying the .text section of a .o file out so there's probably some label stuff. I might be able to pre-process the jumps to convert them? I was able to get a fizzbuzz to run but only because an O3 fizzbuzz doesn't actually have any branches. -O0 fizzbuzz got stuck.

9 notes

·

View notes

Text

OOOh, some hot new chips just dropped into our mailbox - ESP32-P4! 🔥🚀

Espressif's latest chip has a snazzy eval board, and we just snagged a couple for CircuitPython development. The P4 is a RISC V dual core 400MHz processor with CSI/DSI support, USB HS, and Ethernet too. This chip doesn't have BLE or WiFi like all the other ESP chips. Instead, it uses a low-cost ESP32-C5 module as a wireless co-processor. The eval board is sorta shaped like a Raspberry Pi and has various A/V connections. We also got 100 sample chips of the 16MB in-package PSRAM variety, so we can start designing our first board. Shall we do a Feather? a Metro? maybe a Pi Zero-shaped thingy?

#espressif#esp32#ESP32P4#espfriends#adafruit#greetz#circuitpython#hardwaredesign#microcontroller#techinnovation#riscv#developmentboard#diyelectronics#opensourcehardware#embeddedsoftware#chipdesign

3 notes

·

View notes

Text

Rocky Linux 10 Will Support RISC-V

https://rockylinux.org/news/rockylinux-support-for-riscv

0 notes

Text

RISC-V GPU Advances to Manage CPU and NPU Tasks

A new RISC-V microprocessor is capable of handling CPU, GPU, and NPU tasks concurrently. A novel RISC-V micro processing chip design has been developed by X-Silicon Inc. (XSI) that integrates a RISC-V CPU core, RISC-V GPU acceleration, and vector capabilities onto a single device.

According to Jon Peddie Research, the CPU/GPU hybrid device is open-standard and would presumably be open-source as well. It is intended to perform a range of tasks, such as artificial intelligence (AI), that would typically be performed by dedicated CPUs and GPUs. The problem is that it is meant to accomplish all of this with significantly greater efficiency.

The new hybrid CPU/GPU is intended to be a “jack of all trades” machine. JPR claims that the industry has been looking for an open-standard RISC-V GPU that is adaptable and scalable enough to serve a range of sectors, such as IoT devices, virtual reality, and cars. The goal of this new RISC-V CPU and RISC-V GPU is to give manufacturers an open chip architecture that can handle whatever workload they want.

The chip from X-Silicon is unique from previous architectures since it integrates a GPU and CPU into a single-core architecture. This isn’t like the standard AMD and Intel designs, which have distinct GPU and CPU cores. Rather, the core is built to be able to handle tasks on both the CPU and the GPU. It sounds a lot like Intel’s shelved Lara Bee project in that regard, which tried to employ x86 for workloads such as graphics.

The chip makes use of the C-GPU architecture from X-Silicon, which combines GPU acceleration with a vector CPU core that is RISC-V. A 32-bit FPU and Scalier ALU are located in the RISC-V vector core of the architecture. Thread scheduler, Pasteurizer, Clipping Engine, Texture Unit, Neural Engine, and Pixel Processor are some of its features. The device is designed to handle applications such as 2D and 3D graphics, geometric computation, AI, and high-performance computing (HPC).

Theoretically, X-Silicon’s hybrid chip has numerous benefits due to its ability to process both CPU and RISC-V GPU code within its single core. The chip runs a single instruction stream on the open-standard RISC-V ISA for both the CPU and GPU. This results in higher performance and low-memory footprint execution since there is no data copying between the GPU and CPU memory spaces.

Manufacturers can increase processing power as needed by combining the CPU and RISC-V GPU cores into a multi-core design. A fast fabric is used to connect several cores that are tiled across a chip in a multi-core configuration. This also has fast on-chip SRAM or e DRAM caches, which function as an L2 cache capable of combining data from several cores. When necessary, each core can be scheduled to execute workloads unrelated to the others, such as physics, AI, graphics, video, and HPC.

RISC-V GPU

This architecture may allow X-Silicon’s C-GPU architecture to handle any kind of CPU or GPU workload. It is claimed by X-Silicon that Vulkan graphics API is already functioning with “fused RISC-V GPU acceleration.” This ought to be quite beneficial for its advancement and uptake on Android gadgets.

Unlike x86 and ARM, the new design is based on RISC-V, which means that anyone can use the architecture without having to pay instruction-set license fees. The chips could revolutionize the microprocessor business if they function as planned. Theoretically, what X-Silicon claims to have built is more versatile and competent than the existing conventional designs.

Although workloads from both CPUs and RISC-V GPU can be handled by a new RISC-V micro processor, the following summarizes the main distinctions between them:

Building A RISC-V CPU Core

All-purpose: Designed to perform an extensive range of functions, such as multitasking, managing system resources, and executing applications.

Sequential processing: Carries out commands one at a time. more effective when dealing with complicated branching and logic tasks.

Fewer cores: Usually has fewer cores (four to sixteen) that are better suited to specific activities.

Graphics Processing Unit:

Specialized processor: Made to handle graphics and video data quickly, especially for jobs requiring a lot of data to be processed in parallel.

Parallel processing: Is perfect for tasks involving repetitive procedures because it can handle multiple calculations at once.

More cores: Frequently contains a sizable number of parallel processing-optimized cores, in the hundreds or even thousands.

CPU vs GPU Upgrade

CPU: Comparable to an experienced chef who manages several meals at once, alternating between them and making sure each is prepared to perfection. GPU: Similar to a group of line cooks who work together to efficiently prepare big amounts of food by assigning each person to a specialized duty on an assembly line. Even if the RISC-V chip you described is capable of handling both workloads, for best results, it’s critical to grasp the advantages and disadvantages of each type of CPU.

Read more on Govindhtech.com

#CPU#GPU#NPU#RISCV#riscvgpu#microprocessor#govindhtech#news#technews#technologynews#technology#technologytrends

1 note

·

View note

Text

CSE12 Lab 3: Looping in RISC-V Assembly Solved

Minimum Submission Requirements Ensure that your Gradescope submission contains the following file: ○ Lab3.asm Objective This lab will introduce you to the RISC-V assembly language programming using RARS (RISCV Assembler and Runtime Simulator). You will write a program with nested loops in the provided file Lab3.asm to write a specific pattern to a file by the name of lab3_output.txt…

0 notes

Text

biting you back :33

also @transfinite-recursion @gender-conflicted @watermelon-but-awesome @umbraxien @riscv-lesbianism @q4os-tde-official (tagging you again, sorry hehe)

thank y'all so much for being here for me when I needed friends the most. you are the best ♡♡♡

sry if I missed someone, brain's still a bit foggy. but I really love all my mutuals ♡

#if you dont want bites im kissing you#on the lips#>:3c#still not feeling amazing#but im doing better thanks to y'all

41K notes

·

View notes

Text

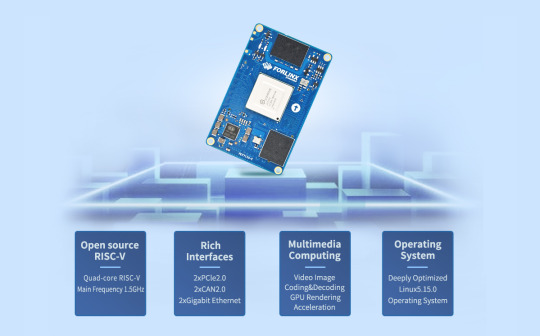

Unveiling the innovative Forlinx FET7110-C System on Module!

🚀 With a powerful quad-core 1.5GHz RISC-V JH7110 processor, advanced GPU, and dynamic power control, it's tailor-made for demanding industrial vision applications like computer vision, deep learning, and graphics rendering.

Elevate your projects with cutting-edge technology!

0 notes

Text

IIT Madras and ISRO Unveil IRIS, India’s First Aerospace-Grade Semiconductor | Daily Reports Online

The Indian Institute of Technology Madras (IIT Madras) and the Indian Space Research Organisation (ISRO) have successfully developed and booted an aerospace-grade semiconductor chip, marking a significant step towards self-reliance in space technology. The chip, named ‘IRIS’ (Indigenous RISCV Controller for Space Applications), has been designed based on the SHAKTI processor and is intended for…

0 notes