#FPGA Design Flow

Explore tagged Tumblr posts

Text

The Department of Electronics and Communication Engineering K.Ramakrishnan College of Technology, in association with the IEEE Student Branch, recently organized an insightful invited talk on “Demystifying FPGA Design: From Concept to Implementation.” Further, this event, featured Dr.M.Elangovan, Associate Professor, Department of Electronics & Communication Engineering, Government College of Engineering, Trichy. Moreover, nearly 122 third-year students from our department attended the session, actively participated, and greatly benefited from the expert insights shared.

For more interesting information CLICK HERE

#the best engineering college krct#quality engineering and technical education.#best college of technology in trichy#krct the best college of technology in trichy#k ramakrishnan college of technology trichy#top college of technology in trichy#best autonomous college of technology in trichy#the best college for b.tech#ECE Talk session on Demystifying FPGA Design at KRCT#What is FPGA?#Applications of FPGA Design#FPGA Design Flow#Programming the FPGA

0 notes

Text

1 note

·

View note

Text

AMD Versal AI Engine: Powering Next-Gen Intelligence

What is Versal AI engine?

The Versal Premium line, which integrates AI Engines, has exceptional adaptive signal processing capability and is designed for the most demanding compute and data transportation applications in wired communications, data center computation, test and measurement, and aerospace and military.

Versal AI Engine

The AI Engine Array Interface may be configured with to the AMD LogiCORE AI Engine IP. Through tiles included in the AI Engine Array Interface, this array is linked to both the Network on Chip and the programmable logic (PL). This IP specifies the clock controlling the AI Engine array and permits the definition of the number of AXI4-Stream and memory-mapped AXI interfaces with their corresponding width and orientation.

Key Features and Benefits

AXI4 configuration interfaces that are memory mapped.

AXI4 master interfaces that are memory mapped.

AXI4-Stream master and slave interfaces having 32, 64, or 128 bit data widths that may be adjusted.

Fast streams may be enabled by choosing to enable registered interfaces.

Programmable logic (PL) stream clocks automatically associate.

Designing AMD Versal AI Engine

Image Credit To AMD

AMD Developing Versal AI Engine with Vitis Model Composer AMD With Vitis Model Composer, algorithms designed for Versal AI Engines may be quickly simulated, explored, and coded from inside the Simulink environment. This may be accomplished by importing kernels and data-flow graphs into Vitis Model Composer as blocks and adjusting the block GUI parameter to control the behavior of the kernels and graphs, or by utilizing the AI Engine library blocks.

Additionally, the tool lets you use a combination of AI Engine and programmable logic (HDL/HLS) blocks to create and simulate a design. By seamlessly integrating Vitis Model Composer AI Engine blocks with Simulink source and sink blocks, simulation results may be viewed.

For usage in the Simulink environment, Vitis Model Composer offers a collection of blocks that are optimized for speed. These consist of:

AI Engine blocks

Image Credit To AMD

Comprises a collection of intricate AI Engine DSP building elements pertaining to mixers, FIR, FFT, and DDS.

includes blocks for importing graphs and kernels that may be directed to Versal devices’ AI Engine section.

HLS (Targeting PL and generates HLS code)

Targeting PL and producing HLS code, HLS provides preset blocks that contain bit-wise operations, logic, linear algebra, and math functional blocks.

Block the import of HLS kernels that are intended for Versal devices’ PL section.

HDL (Produces RTL code and targets PL)

Blocks for modeling and synthesizing DSP, arithmetic, and logic components on an FPGA

contains a FIR Compiler block that targets the Versal design’s specific DSP48E1 and DSP48E2 hardware resources.

Blocks that facilitate communication between the AMD HDL blockset and the AI Engine.

Unleash DSP Compute with AMD Versal AI Engines

For next-generation DSP workloads, speed up demanding high-performance DSP applications.

AMD Versal AI Engine Technology Enables High-Performance Digital Signal Processing (DSP) Requirements

Clients developing next-generation DSP applications need enormous computational power, which conventional FPGA designs cannot effectively provide. Large quantities of DSP blocks and programmable logic resources may be used by compute-intensive DSP applications like FIR, FFT, and General Matrix Multiply.

The total computation capability that conventional programmable logic devices may provide may be greatly diminished by this need. For demanding DSP workloads with stringent power constraints, just expanding the number of DSP blocks and programmable logic available is not a scalable solution.

In these situations, Versal AI Engines are intended to provide a more effective computing solution.

Boost Compute and Use Less Power

Optimize performance and transform your DSP designs.

Did you know that you may increase scalability and efficiency to satisfy the growing needs of high-performance, next-generation DSP applications? Learn 5 strategies to improve your DSP designs using AMD Versal AI Engines.

Access Benchmarks Comparing Versal AI Engines to Previous Programmable Logic Technology

Please get in touch with sales or your FAE for test results and source designs for head-to-head benchmark comparisons between designs that use just Programmable Logic and adaptable SoC + AI Engine designs that use AMD Versal adaptable SoCs.

Get Started with Versal AI Engines for DSP

Increase DSP compute density for the next generation of demanding DSP workloads by speeding up the most demanding high-performance DSP applications.

Read more on govindhtech.com

#AMDVersalAIEngine#PoweringNextGenIntelligence#AIEngine#FPGA#AMDVersal#KeyFeatures#AMD#DesigningAMD#AIEngineblocks#DSPCompute#technology#technews#news#govindhtech

2 notes

·

View notes

Text

Understanding FPGA Architecture: Key Insights

Introduction to FPGA Architecture

Imagine having a circuit board that you could rewire and reconfigure as many times as you want. This adaptability is exactly what FPGAs offer. The world of electronics often seems complex and intimidating, but understanding FPGA architecture is simpler than you think. Let’s break it down step by step, making it easy for anyone to grasp the key concepts.

What Is an FPGA?

An FPGA, or Field Programmable Gate Array, is a type of integrated circuit that allows users to configure its hardware after manufacturing. Unlike traditional microcontrollers or processors that have fixed functionalities, FPGAs are highly flexible. You can think of them as a blank canvas for electrical circuits, ready to be customized according to your specific needs.

How FPGAs Are Different from CPUs and GPUs

You might wonder how FPGAs compare to CPUs or GPUs, which are more common in everyday devices like computers and gaming consoles. While CPUs are designed to handle general-purpose tasks and GPUs excel at parallel processing, FPGAs stand out because of their configurability. They don’t run pre-defined instructions like CPUs; instead, you configure the hardware directly to perform tasks efficiently.

Basic Building Blocks of an FPGA

To understand how an FPGA works, it’s important to know its basic components. FPGAs are made up of:

Programmable Logic Blocks (PLBs): These are the “brains��� of the FPGA, where the logic functions are implemented.

Interconnects: These are the wires that connect the logic blocks.

Input/Output (I/O) blocks: These allow the FPGA to communicate with external devices.

These elements work together to create a flexible platform that can be customized for various applications.

Understanding Programmable Logic Blocks (PLBs)

The heart of an FPGA lies in its programmable logic blocks. These blocks contain the resources needed to implement logic functions, which are essentially the basic operations of any electronic circuit. In an FPGA, PLBs are programmed using hardware description languages (HDLs) like VHDL or Verilog, enabling users to specify how the FPGA should behave for their particular application.

What are Look-Up Tables (LUTs)?

Look-Up Tables (LUTs) are a critical component of the PLBs. Think of them as small memory units that can store predefined outputs for different input combinations. LUTs enable FPGAs to quickly execute logic operations by “looking up” the result of a computation rather than calculating it in real-time. This speeds up performance, making FPGAs efficient at performing complex tasks.

The Role of Flip-Flops in FPGA Architecture

Flip-flops are another essential building block within FPGAs. They are used for storing individual bits of data, which is crucial in sequential logic circuits. By storing and holding values, flip-flops help the FPGA maintain states and execute tasks in a particular order.

Routing and Interconnects: The Backbone of FPGAs

Routing and interconnects within an FPGA are akin to the nervous system in a human body, transmitting signals between different logic blocks. Without this network of connections, the logic blocks would be isolated and unable to communicate, making the FPGA useless. Routing ensures that signals flow correctly from one part of the FPGA to another, enabling the chip to perform coordinated functions.

Why are FPGAs So Versatile?

One of the standout features of FPGAs is their versatility. Whether you're building a 5G communication system, an advanced AI model, or a simple motor controller, an FPGA can be tailored to meet the exact requirements of your application. This versatility stems from the fact that FPGAs can be reprogrammed even after they are deployed, unlike traditional chips that are designed for one specific task.

FPGA Configuration: How Does It Work?

FPGAs are configured through a process called “programming” or “configuration.” This is typically done using a hardware description language like Verilog or VHDL, which allows engineers to specify the desired behavior of the FPGA. Once programmed, the FPGA configures its internal circuitry to match the logic defined in the code, essentially creating a custom-built processor for that particular application.

Real-World Applications of FPGAs

FPGAs are used in a wide range of industries, including:

Telecommunications: FPGAs play a crucial role in 5G networks, enabling fast data processing and efficient signal transmission.

Automotive: In modern vehicles, FPGAs are used for advanced driver assistance systems (ADAS), real-time image processing, and autonomous driving technologies.

Consumer Electronics: From smart TVs to gaming consoles, FPGAs are used to optimize performance in various devices.

Healthcare: Medical devices, such as MRI machines, use FPGAs for real-time image processing and data analysis.

FPGAs vs. ASICs: What’s the Difference?

FPGAs and ASICs (Application-Specific Integrated Circuits) are often compared because they both offer customizable hardware solutions. The key difference is that ASICs are custom-built for a specific task and cannot be reprogrammed after they are manufactured. FPGAs, on the other hand, offer the flexibility of being reconfigurable, making them a more versatile option for many applications.

Benefits of Using FPGAs

There are several benefits to using FPGAs, including:

Flexibility: FPGAs can be reprogrammed even after deployment, making them ideal for applications that may evolve over time.

Parallel Processing: FPGAs excel at performing multiple tasks simultaneously, making them faster for certain operations than CPUs or GPUs.

Customization: FPGAs allow for highly customized solutions, tailored to the specific needs of a project.

Challenges in FPGA Design

While FPGAs offer many advantages, they also come with some challenges:

Complexity: Designing an FPGA requires specialized knowledge of hardware description languages and digital logic.

Cost: FPGAs can be more expensive than traditional microprocessors, especially for small-scale applications.

Power Consumption: FPGAs can consume more power compared to ASICs, especially in high-performance applications.

Conclusion

Understanding FPGA architecture is crucial for anyone interested in modern electronics. These devices provide unmatched flexibility and performance in a variety of industries, from telecommunications to healthcare. Whether you're a tech enthusiast or someone looking to learn more about cutting-edge technology, FPGAs offer a fascinating glimpse into the future of computing.

2 notes

·

View notes

Text

Mastering VLSI: Why the Right Training Matters for a Thriving Tech Career

The Rising Demand for VLSI Experts The modern world is driven by electronics. From smartphones to smart cars, every innovation depends on microchips designed using VLSI (Very Large Scale Integration) technology. With the growing use of AI, IoT, and automation, the need for skilled VLSI professionals has increased rapidly. This makes VLSI an essential field for those looking to build a strong career in electronics and semiconductor industries. Choosing the right learning path is key to making the most of this opportunity.

Exploring the Benefits of VLSI Online Training Courses Many learners today seek flexible and effective ways to upskill. VLSI online training courses offer an excellent solution by combining convenience with quality education. These courses provide access to experienced instructors, practical assignments, and industry-based projects—all from the comfort of home. Learners can grasp digital design, physical design, verification, and ASIC/FPGA concepts without sacrificing their job or academic responsibilities. The online model also allows repeated learning and flexible scheduling, making it ideal for beginners as well as professionals wanting to upgrade their knowledge.

Choosing the Right Learning Mode While online learning provides flexibility, some individuals prefer classroom-based teaching for real-time interaction and immediate doubt clearing. The choice between online and offline modes largely depends on individual preferences, learning habits, and career goals. However, what truly matters is the quality of the training and the expertise of the instructors involved.

Key Skills Taught in VLSI Training A well-structured VLSI course should cover areas like CMOS technology, HDL languages such as Verilog and VHDL, physical design flow, and functional verification techniques. Practical exposure through lab sessions or simulation tools is crucial. Additionally, learners should be guided on real-time projects to apply their theoretical knowledge to industry problems.

Why VLSI Coaching in Hyderabad is Gaining Popularity Hyderabad has become a major hub for semiconductor and electronics industries. As a result, VLSI coaching in Hyderabad has gained recognition for producing skilled professionals. Reputed training centers in the city offer tailored coaching with an industry-aligned curriculum, experienced faculty, and placement support. Many aspirants from across the country travel to Hyderabad to benefit from this coaching environment that bridges academic learning with industry demands.

Conclusion VLSI technology plays a vital role in shaping the electronics and semiconductor industries. Whether through VLSI online training courses or classroom-based programs like VLSI coaching in Hyderabad, acquiring the right skills is essential for career growth. Institutions like Takshila Institute of VLSI Technologies provide training that matches industry standards, helping learners succeed in a competitive field. The choice of platform and location may differ, but the goal remains the same—building a strong foundation in VLSI for a successful future.

0 notes

Text

Paving the Way for Chip Design Excellence: A Deep Dive into VLSI Training in India

The Growing Significance of VLSI in Modern Technology

In the fast-paced world of semiconductors and microelectronics, VLSI (Very Large Scale Integration) has become the backbone of modern digital devices. From smartphones and laptops to high-speed routers and IoT devices, VLSI plays a pivotal role in designing and manufacturing the integrated circuits that power these innovations. As the demand for compact, power-efficient, and high-performance chips increases, so does the need for skilled VLSI professionals. The global push towards AI, 5G, and advanced computing systems only amplifies this necessity, making VLSI a highly sought-after skill in the electronics industry.

India, with its robust engineering talent and flourishing technology ecosystem, has emerged as a critical player in the global semiconductor landscape. Government initiatives like “Make in India” and “India Semiconductor Mission” are catalyzing local chip design and fabrication capabilities. This surge in national focus on electronics manufacturing has naturally heightened the demand for high-quality VLSI training institutes across the country. For aspiring engineers and professionals seeking a sustainable and rewarding career, VLSI training offers a direct pathway into one of the most dynamic and high-growth sectors in technology today.

The Core Components of a Quality VLSI Training Program

A well-structured VLSI training program encompasses both theoretical concepts and practical exposure to industry-standard tools and methodologies. Topics typically covered include digital and analog circuit design, semiconductor physics, system-on-chip (SoC) architecture, FPGA prototyping, verification methodologies, and ASIC design flow. These subjects provide a comprehensive understanding of how integrated circuits are conceptualized, designed, simulated, and fabricated. However, what truly differentiates a top-tier training institute is its ability to combine academic rigor with hands-on experience through projects and tool-based learning.

Moreover, students and professionals benefit immensely from training centers that have strong industry linkages and offer mentorship from experienced professionals. Faculty members who have spent years in semiconductor companies bring real-world challenges into the classroom, bridging the gap between textbook knowledge and industry requirements. Labs equipped with EDA tools like Cadence, Synopsys, and Mentor Graphics ensure learners are industry-ready upon graduation. In cities like Bangalore—known as India’s Silicon Valley—the top 10 VLSI institutes in Bangalore often incorporate job-oriented modules and offer placement support, making them a preferred choice among aspiring chip designers.

What Sets the Best Institutes Apart?

When evaluating the best VLSI training institute in India, several factors come into play: curriculum relevance, faculty expertise, infrastructure quality, placement support, and student reviews. Institutes that frequently update their course content to align with the rapidly evolving semiconductor industry trends hold a competitive edge. Additionally, institutes that integrate internship opportunities and real-time project work provide learners with the practical exposure necessary to thrive in job roles such as physical design engineer, verification engineer, or design-for-testability expert.

Soft skills training, resume preparation workshops, and mock interviews also form a crucial part of the training experience. These non-technical modules play a significant role in enhancing the employability of students. The best institutes also actively engage with the VLSI community by hosting guest lectures, webinars, and tech-talks from leaders in the semiconductor domain. Such activities not only enrich the learning environment but also offer networking opportunities that can prove valuable during job searches or career transitions. By focusing on holistic skill development, these institutes ensure their students are well-prepared to meet the real-world demands of chip design and development.

Career Opportunities and Industry Demand

With the rise in global demand for advanced chips, career opportunities in VLSI are more abundant than ever. Major semiconductor giants like Intel, Qualcomm, Texas Instruments, and AMD have established significant R&D and design centers in India, especially in Bangalore, Hyderabad, and Noida. This has created a fertile job market for trained professionals skilled in digital design, verification, layout, and physical design. Moreover, the Indian government's push for indigenous chip production has led to the rise of several startups and fabless companies, adding further momentum to hiring in this space.

Candidates who have completed rigorous VLSI training programs find themselves eligible for diverse roles across design, testing, and verification verticals. Entry-level engineers may start as interns or trainees but can quickly progress to mid-level roles with hands-on experience and continued learning. As artificial intelligence, edge computing, and high-performance computing continue to evolve, the skill sets offered by VLSI training are increasingly becoming foundational to building the next generation of smart and connected devices. Hence, investing in a high-quality VLSI education can be a strategic move for any engineering graduate or tech professional looking to future-proof their career.

Choosing the Right Path Forward

Given the numerous institutes offering VLSI training, selecting the right one can significantly influence a learner’s career trajectory. Prospective students should look beyond flashy marketing and focus on tangible outcomes such as placement statistics, alumni success stories, and industry collaborations. Visiting the campuses, speaking to current students, and attending demo sessions can provide better insight into an institute’s strengths and teaching approach. It's essential to choose an institute that not only teaches but also inspires and equips students to excel in a highly competitive domain.

One such reputed institution making strides in the VLSI training landscape is accessible via takshila-vlsi.com. With a blend of cutting-edge curriculum, experienced faculty, and robust placement support, it stands as a noteworthy contender among VLSI training centers in India. Whether you're an engineering graduate aiming for a breakthrough role or a working professional looking to switch domains, structured training in VLSI can be the catalyst for a high-growth career in semiconductors.

0 notes

Text

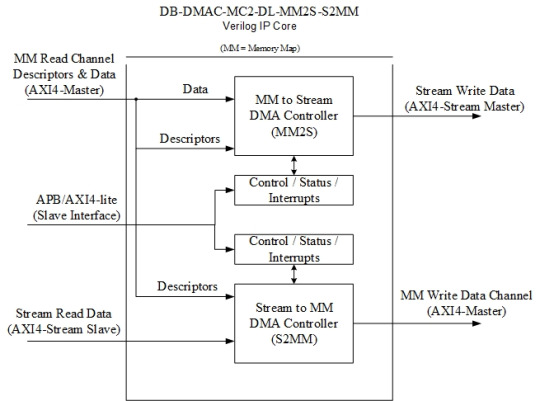

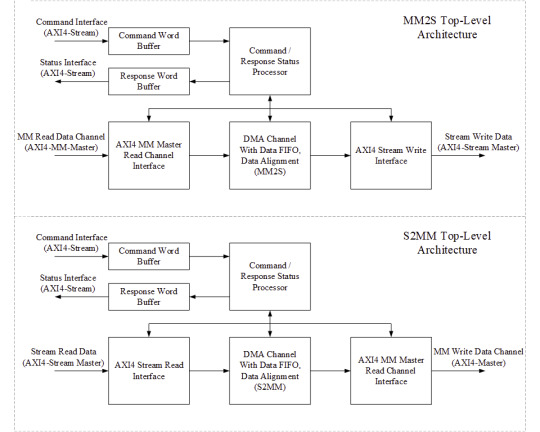

Reducing Latency in Real-Time Applications with AXI4 Stream DMA

In real-time systems, every microsecond counts. Industries like telecommunications, automotive, medical, and defense demand instant data movement between processing units. Any delay can affect performance, accuracy, or safety. Digital Blocks, through its advanced design of AXI4 Stream DMA, is addressing this demand with precision and efficiency.

The Need for High-Speed Data Transfer

Real-time applications depend on the continuous and rapid flow of data. Tasks such as video processing, sensor fusion, and control systems require minimal delay between data capture and action. Standard memory-mapped data transfers often introduce latency due to handshaking, memory access, and software intervention. This slows down systems that must respond without delay.

The AXI4 Stream DMA developed by Digital Blocks helps bypass these barriers. It supports direct data transfers between sources and destinations with minimal CPU involvement. This makes it ideal for applications that require predictable and fast performance.

How AXI4 Stream DMA Improves System Speed

The AXI4 Stream DMA core is built to handle large volumes of data at high speed. It supports streaming data interfaces, where information is transferred in a continuous flow. This design reduces the overhead of individual memory transactions and avoids congestion that slows down traditional DMA systems.

By handling data transfers autonomously, the AXI4 Stream DMA allows the processor to focus on higher-level tasks. Digital Blocks has designed this module to be both lightweight and powerful, ensuring it fits into a wide range of system-on-chip (SoC) designs without consuming unnecessary resources.

Scalability for Complex Applications

Real-time systems vary in size and function. Some may require small and frequent data packets, while others need high-bandwidth continuous streaming. Digital Blocks addresses this need through a scalable AXI4 Stream DMA solution. It supports configurable parameters to match system architecture and data flow requirements.

Developers working on multi-core designs or FPGA-based systems can integrate AXI4 Stream DMA to improve performance while keeping latency under control. The design supports burst transfers, flow control, and error detection, all key features that enhance reliability.

Proven in Real-World Applications

Digital Blocks has delivered its AXI4 Stream DMA core to customers across multiple sectors. In each case, the goal was clear: reduce latency and improve data throughput without compromising system stability. Applications such as real-time video encoding, radar signal processing, and industrial automation have shown marked improvements after adopting this design.

By focusing on a robust, standards-based solution, Digital Blocks ensures that the AXI4 Stream DMA integrates smoothly with existing AXI-based systems. This reduces the time and cost of development while improving end-product performance.

Building the Future of Low-Latency Systems

Latency will always be a concern in real-time systems. However, the right architecture can bring it within acceptable limits. The AXI4 Stream DMA by Digital Blocks provides a focused solution to this challenge. With careful design and proven efficiency, it supports the fast, consistent data flow that modern systems demand.

As real-time applications continue to grow in complexity, Digital Blocks remains committed to delivering high-performance solutions that keep pace with future needs. More details visit us

#ahb dma controller#axi4 stream dma#axi bridge ip core#axi dma controller ip#ahb dma verilog#axi dma scatter gather#axi dma ip core#axi dma verilog#axi4 data mover#axi stream dma

0 notes

Text

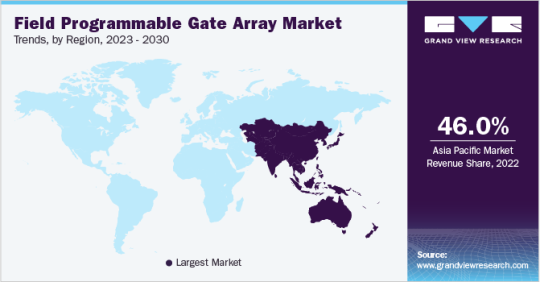

Are You Ready? The Field Programmable Gate Array Market is Exploding!

Field Programmable Gate Array (FPGA) Industry Overview

The global Field Programmable Gate Arrays (FPGAs) Market was valued at $10.46 billion in 2022 and is projected to expand at an annual rate of 10.8% from 2023 to 2030. The increasing adoption of field programmable gate arrays in applications such as deep packet inspection, network processing, and security is expected to fuel their demand throughout the forecast period. The preference for FPGA architecture is growing due to its advantages, including low power consumption and high compute density. This trend is being driven by the rising need for efficient data flow and streaming data processing across various applications. For example, in February 2022, QuickLogic Corporation introduced PolarPro 3 to address the shortage of low-power FPGAs. This product is designed for ultra-low power consumption, making it ideal for wearables, handheld devices, and mobile applications. Such product launches by key industry players are anticipated to drive market growth over the forecast period.

Detailed Segmentation:

Type Insights

Mid-range FPGAs are expected to register the highest CAGR of 12.5% over the forecast period, owing to the properties offered by the segment such as low power consumption, small form factor, and high performance for FPGA-based devices. In addition, the advantages of the mid-range type segment that are capable of delivering a significant digital signal processing (DSP) along with embedded memory to logic ratio that enhances the intelligence for several applications is anticipated to drive the segment growth.

Application Insights

The military and aerospace segment is expected to expand at the fastest CAGR of 12.7% over the forecast period. Emergence of embedded field programmable gate array has particularly favored the aviation and defense industry by offering even better integration, reliability, and low power option over the traditional FPGAs, which is expected to drive the military and aerospace segment growth during the forecast period.

Technology Insights

Flash-based FPGAs are expected to register the fastest growth rate of 11.3% over the forecast period. The segment is witnessing high demand as major players upgrade their portfolios of FPGAs to cater to the growing demand from the expanding application base. Additionally, the rising trend favoring flash-based FPGAs over SRAM-based FPGAs due to their lower power consumption is also boosting the segment growth. The utilization of non-volatile flash memory for configuration storage eliminates the need for continuous power, aligning with the industry's emphasis on energy efficiency and power optimization. This power-saving feature is particularly advantageous in battery-powered devices, portable electronics, and energy-constrained applications, which is expected to drive the market growth over the forecast period.

Regional Insights

The South America region is expected to register a significant growth rate of 11.9% over the forecast period. This growth is attributed to the boost in the automobile, industrial, and aerospace sector, where the application of FPGA-based solutions is substantial, especially in Brazil. In addition, the growing demand for connectivity in the region is expected to augment the adoption of advanced telecommunications infrastructure along with the expansion of broadband networks, which is expected to drive the growth of the field programmable gate array market across the region.

Gather more insights about the market drivers, restraints, and growth of the Field Programmable Gate Array (FPGA) Market

Key Companies & Market Share Insights

The market is classified as highly competitive, with the presence of several field programmable gate array market players. The key players operating in the field programmable gate array industry are focusing on strategic alliances, mergers & acquisitions, expansion, and product development to remain competitive in the industry. For instance, in May 2023, Intel Corporation launched their new FPGAs, the Agilex 7 FPGAs with R-Tile. This product from the company is expected to be the first FPGA with CXL and PCIe 5.0 capabilities. Such developments are expected to propel the field programmable gate array market growth over the forecast period. Some of the major players in the global field programmable gate array (FPGA) market:

Intel Corporation

Xilinx, Inc.

Qualcomm Technologies, Inc.

NVIDIA Corporation

Broadcom

AMD, Inc.

Quicklogic Corporation

Lattice Semiconductor Corporation

Achronix Semiconductor Corporation

Microchip Technology Inc.

Order a free sample PDF of the Market Intelligence Study, published by Grand View Research.

0 notes

Text

VLSI Design And Verification Course For Fresher - VLSI Guru

In the fast-paced world of technology, the VLSI (Very Large Scale Integration) domain stands as a cornerstone for innovations in electronics and semiconductor design. If you’re a fresher aiming to dive into this exciting field, the VLSI Design and Verification Course by VLSI Guru is your perfect launchpad.

Why Choose VLSI as a Career Path?

The demand for skilled professionals in VLSI design and verification is skyrocketing, with industries relying on advanced ASIC (Application-Specific Integrated Circuits) and FPGA (Field-Programmable Gate Arrays) to power cutting-edge technologies. From smartphones to autonomous vehicles, the scope of VLSI is vast and evolving.

What Does the Course Offer?

The VLSI Design and Verification Course by VLSI Guru is tailored for freshers, focusing on:

HDL Languages: Master Verilog and VHDL for RTL coding.

SystemVerilog & UVM: Learn modern verification methodologies for building robust testbenches.

ASIC Design Flow: Gain insights into the complete chip design process.

FPGA Prototyping: Get hands-on experience with FPGA tools and workflows.

Debugging & Tools Expertise: Work with industry-standard tools like Cadence, Synopsys, and Mentor Graphics.

Why VLSI Guru?

VLSI Guru emphasizes practical learning through real-world projects and labs. Freshers are trained to handle challenges in semiconductor design and verification, bridging the gap between academia and industry.

Who Can Enroll?

The course is ideal for engineering graduates in ECE, EE, or CSE with a passion for chip design and a desire to work in leading semiconductor companies.

Start your journey in the semiconductor industry today with VLSI Guru's specialized training.

0 notes

Text

Vivado Support with IDesignSpec Suite- Agnisys

IDesignSpecTM (IDS) is a product suite that improves the productivity of FPGA/ASIC, IP/SoC, and system development teams. These products encompass an innovative register information management system to capture hardware functional specifications and addressable register specifications in a single executable specification. All downstream code and documentation for the addressable registers, sequences, or interrupts can be generated from this single specification along with validation in Xilinx Vivado Environment.

Vivado is a tool developed by Xilinx for creating digital designs. Vivado facilitates developers checking their designed RTL correctness and validating it in a hardware platform with different vendor’s boards containing Xilinx FPGAs. Currently, Zynq7000 family is used like Artix-7, Kintex-7 etc.. These special devices have two parts, the Programmable Logic (PL) block and the Processing System (PS) block. PL is used to implement RTL and PS is used for embedded applications oriented to ARM processors using Embedded C.

The following problems can be solved by IDesignSpec when generating outputs for Vivado:

Simplified RTL implementation:

Users do not need to worry about the RTL implementation. IDS takes care of generating the necessary RTL code.

Pre-validated RTL:

Users do not need to validate the RTL at their end because the IDS-generated RTL is already validated.

The following process achieves these results.

As shown in Figure 1 below, RTL output can be generated by the Agnisys cross platform GUI by going to the configuration window and selecting the desired output:

Users can generate the following two files from IDesignSpec:

RTL output file

AXI widget file

Flow of Process Execution:

This process is divided into two parts:

Create package IP

Generate bitstream with Zynq Processing System

Create Package IP:

The process to create package IP is shown below

Generate Bitstream:

Generate the bitstream with Zynq Processing System as shown below:

The generated bitstream is used to program the FPGA and run on the hardware. Vivado is built with an SDK for running projects based on C applications.

Application Example:

A typical application on the hardware platform, Zedboard, using both Vivado and SDK with IDesignSpec-GDI and IDS-Validate is shown below:

Action register, extra register, parity, and sniffer code are generated by IDS.

Cosmic code, which is hard-coded, will induce errors in registers through the switch.

Parity and sniffer will detect errors in registers and send a signal to an error LED. This is part of the Vivado implementation.

IDS-Validate generated C files are executed by the Zynq Processor through the Software AXI Interface, sending signals to the PCB according to the application. This is part of the SDK.

Conclusion:

With the help of the IDesignSpec Suite, users can create embedded projects very easily. There is no burden of writing HDL files and C programs for specific application projects.

Call for action: To get more information about how we can help you to create Vivado-based projects reach out here.

0 notes

Text

How FPGA-to-FPGA Retargeting Improves Performance and Versatility

1 note

·

View note

Text

Agilex 3 FPGAs: Next-Gen Edge-To-Cloud Technology At Altera

Agilex 3 FPGA

Today, Altera, an Intel company, launched a line of FPGA hardware, software, and development tools to expand the market and use cases for its programmable solutions. Altera unveiled new development kits and software support for its Agilex 5 FPGAs at its annual developer’s conference, along with fresh information on its next-generation, cost-and power-optimized Agilex 3 FPGA.

Altera

Why It Matters

Altera is the sole independent provider of FPGAs, offering complete stack solutions designed for next-generation communications infrastructure, intelligent edge applications, and high-performance accelerated computing systems. Customers can get adaptable hardware from the company that quickly adjusts to shifting market demands brought about by the era of intelligent computing thanks to its extensive FPGA range. With Agilex FPGAs loaded with AI Tensor Blocks and the Altera FPGA AI Suite, which speeds up FPGA development for AI inference using well-liked frameworks like TensorFlow, PyTorch, and OpenVINO toolkit and tested FPGA development flows, Altera is leading the industry in the use of FPGAs in AI inference workload

Intel Agilex 3

What Agilex 3 FPGAs Offer

Designed to satisfy the power, performance, and size needs of embedded and intelligent edge applications, Altera today revealed additional product details for its Agilex 3 FPGA. Agilex 3 FPGAs, with densities ranging from 25K-135K logic elements, offer faster performance, improved security, and higher degrees of integration in a smaller box than its predecessors.

An on-chip twin Cortex A55 ARM hard processor subsystem with a programmable fabric enhanced with artificial intelligence capabilities is a feature of the FPGA family. Real-time computation for time-sensitive applications such as industrial Internet of Things (IoT) and driverless cars is made possible by the FPGA for intelligent edge applications. Agilex 3 FPGAs give sensors, drivers, actuators, and machine learning algorithms a smooth integration for smart factory automation technologies including robotics and machine vision.

Agilex 3 FPGAs provide numerous major security advancements over the previous generation, such as bitstream encryption, authentication, and physical anti-tamper detection, to fulfill the needs of both defense and commercial projects. Critical applications in industrial automation and other fields benefit from these capabilities, which guarantee dependable and secure performance.

Agilex 3 FPGAs offer a 1.9×1 boost in performance over the previous generation by utilizing Altera’s HyperFlex architecture. By extending the HyperFlex design to Agilex 3 FPGAs, high clock frequencies can be achieved in an FPGA that is optimized for both cost and power. Added support for LPDDR4X Memory and integrated high-speed transceivers capable of up to 12.5 Gbps allow for increased system performance.

Agilex 3 FPGA software support is scheduled to begin in Q1 2025, with development kits and production shipments following in the middle of the year.

How FPGA Software Tools Speed Market Entry

Quartus Prime Pro

The Latest Features of Altera’s Quartus Prime Pro software, which gives developers industry-leading compilation times, enhanced designer productivity, and expedited time-to-market, are another way that FPGA software tools accelerate time-to-market. With the impending Quartus Prime Pro 24.3 release, enhanced support for embedded applications and access to additional Agilex devices are made possible.

Agilex 5 FPGA D-series, which targets an even wider range of use cases than Agilex 5 FPGA E-series, which are optimized to enable efficient computing in edge applications, can be designed by customers using this forthcoming release. In order to help lower entry barriers for its mid-range FPGA family, Altera provides software support for its Agilex 5 FPGA E-series through a free license in the Quartus Prime Software.

Support for embedded applications that use Altera’s RISC-V solution, the Nios V soft-core processor that may be instantiated in the FPGA fabric, or an integrated hard-processor subsystem is also included in this software release. Agilex 5 FPGA design examples that highlight Nios V features like lockstep, complete ECC, and branch prediction are now available to customers. The most recent versions of Linux, VxWorks, and Zephyr provide new OS and RTOS support for the Agilex 5 SoC FPGA-based hard processor subsystem.

How to Begin for Developers

In addition to the extensive range of Agilex 5 and Agilex 7 FPGAs-based solutions available to assist developers in getting started, Altera and its ecosystem partners announced the release of 11 additional Agilex 5 FPGA-based development kits and system-on-modules (SoMs).

Developers may quickly transition to full-volume production, gain firsthand knowledge of the features and advantages Agilex FPGAs can offer, and easily and affordably access Altera hardware with FPGA development kits.

Kits are available for a wide range of application cases and all geographical locations. To find out how to buy, go to Altera’s Partner Showcase website.

Read more on govindhtech.com

#Agilex3FPGA#NextGen#CloudTechnology#TensorFlow#Agilex5FPGA#OpenVINO#IntelAgilex3#artificialintelligence#InternetThings#IoT#FPGA#LPDDR4XMemory#Agilex5FPGAEseries#technology#Agilex7FPGAs#QuartusPrimePro#technews#news#govindhtech

2 notes

·

View notes

Text

Understanding FPGA Architecture: Key Insights

Introduction to FPGA Architecture

Imagine having a circuit board that you could rewire and reconfigure as many times as you want. This adaptability is exactly what FPGAs offer. The world of electronics often seems complex and intimidating, but understanding FPGA architecture is simpler than you think. Let’s break it down step by step, making it easy for anyone to grasp the key concepts.

What Is an FPGA?

An FPGA, or Field Programmable Gate Array, is a type of integrated circuit that allows users to configure its hardware after manufacturing. Unlike traditional microcontrollers or processors that have fixed functionalities, FPGAs are highly flexible. You can think of them as a blank canvas for electrical circuits, ready to be customized according to your specific needs.

How FPGAs Are Different from CPUs and GPUs

You might wonder how FPGAs compare to CPUs or GPUs, which are more common in everyday devices like computers and gaming consoles. While CPUs are designed to handle general-purpose tasks and GPUs excel at parallel processing, FPGAs stand out because of their configurability. They don’t run pre-defined instructions like CPUs; instead, you configure the hardware directly to perform tasks efficiently.

Basic Building Blocks of an FPGA

To understand how an FPGA works, it’s important to know its basic components. FPGAs are made up of:

Programmable Logic Blocks (PLBs): These are the “brains” of the FPGA, where the logic functions are implemented.

Interconnects: These are the wires that connect the logic blocks.

Input/Output (I/O) blocks: These allow the FPGA to communicate with external devices.

These elements work together to create a flexible platform that can be customized for various applications.

Understanding Programmable Logic Blocks (PLBs)

The heart of an FPGA lies in its programmable logic blocks. These blocks contain the resources needed to implement logic functions, which are essentially the basic operations of any electronic circuit. In an FPGA, PLBs are programmed using hardware description languages (HDLs) like VHDL or Verilog, enabling users to specify how the FPGA should behave for their particular application.

What are Look-Up Tables (LUTs)?

Look-Up Tables (LUTs) are a critical component of the PLBs. Think of them as small memory units that can store predefined outputs for different input combinations. LUTs enable FPGAs to quickly execute logic operations by “looking up” the result of a computation rather than calculating it in real-time. This speeds up performance, making FPGAs efficient at performing complex tasks.

The Role of Flip-Flops in FPGA Architecture

Flip-flops are another essential building block within FPGAs. They are used for storing individual bits of data, which is crucial in sequential logic circuits. By storing and holding values, flip-flops help the FPGA maintain states and execute tasks in a particular order.

Routing and Interconnects: The Backbone of FPGAs

Routing and interconnects within an FPGA are akin to the nervous system in a human body, transmitting signals between different logic blocks. Without this network of connections, the logic blocks would be isolated and unable to communicate, making the FPGA useless. Routing ensures that signals flow correctly from one part of the FPGA to another, enabling the chip to perform coordinated functions.

Why are FPGAs So Versatile?

One of the standout features of FPGAs is their versatility. Whether you're building a 5G communication system, an advanced AI model, or a simple motor controller, an FPGA can be tailored to meet the exact requirements of your application. This versatility stems from the fact that FPGAs can be reprogrammed even after they are deployed, unlike traditional chips that are designed for one specific task.

FPGA Configuration: How Does It Work?

FPGAs are configured through a process called “programming” or “configuration.” This is typically done using a hardware description language like Verilog or VHDL, which allows engineers to specify the desired behavior of the FPGA. Once programmed, the FPGA configures its internal circuitry to match the logic defined in the code, essentially creating a custom-built processor for that particular application.

Real-World Applications of FPGAs

FPGAs are used in a wide range of industries, including:

Telecommunications: FPGAs play a crucial role in 5G networks, enabling fast data processing and efficient signal transmission.

Automotive: In modern vehicles, FPGAs are used for advanced driver assistance systems (ADAS), real-time image processing, and autonomous driving technologies.

Consumer Electronics: From smart TVs to gaming consoles, FPGAs are used to optimize performance in various devices.

Healthcare: Medical devices, such as MRI machines, use FPGAs for real-time image processing and data analysis.

FPGAs vs. ASICs: What’s the Difference?

FPGAs and ASICs (Application-Specific Integrated Circuits) are often compared because they both offer customizable hardware solutions. The key difference is that ASICs are custom-built for a specific task and cannot be reprogrammed after they are manufactured. FPGAs, on the other hand, offer the flexibility of being reconfigurable, making them a more versatile option for many applications.

Benefits of Using FPGAs

There are several benefits to using FPGAs, including:

Flexibility: FPGAs can be reprogrammed even after deployment, making them ideal for applications that may evolve over time.

Parallel Processing: FPGAs excel at performing multiple tasks simultaneously, making them faster for certain operations than CPUs or GPUs.

Customization: FPGAs allow for highly customized solutions, tailored to the specific needs of a project.

Challenges in FPGA Design

While FPGAs offer many advantages, they also come with some challenges:

Complexity: Designing an FPGA requires specialized knowledge of hardware description languages and digital logic.

Cost: FPGAs can be more expensive than traditional microprocessors, especially for small-scale applications.

Power Consumption: FPGAs can consume more power compared to ASICs, especially in high-performance applications.

Conclusion

Understanding FPGA architecture is crucial for anyone interested in modern electronics. These devices provide unmatched flexibility and performance in a variety of industries, from telecommunications to healthcare. Whether you're a tech enthusiast or someone looking to learn more about cutting-edge technology, FPGAs offer a fascinating glimpse into the future of computing.

0 notes

Text

Top VLSI Institutes in Bangalore and Top 10 VLSI Training Institutes – Takshila Institute

The Takshila Institute of VLSI Technologies in India is recognized as one of the top VLSI institutes in Bangalore, offering industry-focused training for students and professionals aspiring to build a career in Very Large Scale Integration (VLSI) design. With the growing demand for skilled VLSI engineers in the semiconductor industry, high-quality training institutes play a crucial role in bridging the gap between academic knowledge and industry requirements. Takshila Institute of VLSI Technologies stands out as a leading VLSI training provider, offering specialized courses that equip learners with practical skills and real-world experience.

As one of the top 10 VLSI training institutes, Takshila Institute of VLSI Technologies provides comprehensive training programs covering digital design, analog layout, FPGA design, ASIC verification, physical design, and semiconductor fabrication. The curriculum is designed in collaboration with industry experts, ensuring that students gain hands-on experience in EDA tools, RTL coding, verification methodologies, and physical design flow. The institute also offers specialized courses in Verilog, SystemVerilog, UVM, and Python for VLSI, helping students develop expertise in front-end and back-end design.

The top VLSI institute in Bangalore, Takshila Institute of VLSI Technologies, provides state-of-the-art lab facilities, expert faculty guidance, and real-time project work to ensure that students gain practical exposure to modern VLSI design methodologies. The training includes live interactive sessions, hands-on assignments, and industrial case studies, allowing learners to develop a deep understanding of semiconductor technology. The institute focuses on preparing students for job opportunities by offering placement assistance, resume-building support, mock interviews, and internship opportunities.

What makes Takshila Institute of VLSI Technologies one of the top 10 VLSI training institutes is its career-oriented approach and strong industry connections. The institute has a proven track record of placing students in top semiconductor companies, making it a preferred choice for those looking to enter the VLSI industry. Whether you are a fresh graduate, working professional, or career switcher, this institute provides flexible learning options through classroom-based training and online courses.

With a reputation for excellence in VLSI education, Takshila Institute of VLSI Technologies is a trusted name in semiconductor training in India. If you are looking for the top VLSI institute in Bangalore or one of the top 10 VLSI training institutes, Takshila Institute of VLSI Technologies offers the best learning experience to help you succeed in the VLSI industry.

0 notes

Text

Enhancing High-Speed Data Transfers with AXI DMA Scatter-Gather: A Complete Guide!

Efficient data movement is crucial in high-performance computing and embedded systems. AXI DMA Scatter-Gather plays a vital role in optimizing high-speed data transfers, reducing CPU workload, and enhancing overall system efficiency. In this guide, we will explore the fundamentals of AXI DMA Scatter-Gather, its advantages, and how Digital Blocks provides industry-leading solutions to meet your design needs.

Understanding AXI DMA Scatter-Gather

AXI DMA Scatter-Gather is an advanced Direct Memory Access (DMA) technique that enables efficient data transfer across multiple memory locations. Unlike traditional DMA, which moves data in fixed blocks, scatter-gather mode allows data to be transferred dynamically, improving system flexibility and performance.

Key Benefits of AXI DMA Scatter-Gather:

Reduced CPU Overhead: By offloading data movement tasks, it frees up CPU resources for other critical operations.

Increased Data Transfer Efficiency: It minimizes memory fragmentation and optimizes data throughput.

Low-Latency Performance: Ideal for real-time applications requiring high-speed data processing.

Scalability: Supports high-bandwidth applications in networking, video processing, and AI/ML systems.

How AXI DMA Scatter-Gather Works

The Scatter-Gather mechanism in AXI DMA utilizes a descriptor-based architecture, where each descriptor defines the source, destination, and transfer parameters. This enables seamless handling of multiple data chunks without CPU intervention.

The Process Includes:

Descriptor Preparation: The CPU prepares a linked list of descriptors for data movement.

DMA Controller Execution: The AXI DMA engine reads the descriptors and executes transfers autonomously.

Completion Notification: The system receives an interrupt when the transfer is complete, ensuring seamless data flow.

Digital Blocks: Leading the Way in AXI DMA Scatter-Gather Solutions

At Digital Blocks, we specialize in providing silicon-proven AXI DMA Scatter-Gather IP cores designed to enhance the performance of your FPGA, ASIC, and SoC designs. Our high-performance DMA controllers enable efficient, low-latency data movement, making them ideal for applications in networking, automotive, video processing, and artificial intelligence.

Why Choose Digital Blocks?

Proven Expertise: Over two decades of experience in developing high-speed IP cores.

Optimized Performance: Designed for high-throughput, low-latency applications.

Seamless Integration: Fully compatible with industry-standard AXI architectures.

Customizable Solutions: Tailored to meet specific project requirements.

Conclusion

AXI DMA Scatter-Gather is a game-changer in high-speed data transfers, enabling efficient memory management and reducing CPU workload. With Digital Blocks' industry-leading AXI DMA solutions, engineers can accelerate their designs, improve system performance, and achieve faster time-to-market. For More Details:- https://www.digitalblocks.com/axi-dma-verilog-ip-core/

0 notes

Text

Network Processing Unit (NPU) Market Trends and Opportunities: Global Outlook (2023-2032)

Network Processing Unit (NPU) market is a rapidly evolving segment within the broader semiconductor industry, focused on specialized processors designed to handle network traffic efficiently. NPUs are crucial for managing and optimizing data flow in modern communication networks, providing high-speed packet processing, deep packet inspection, and network security functions. They are widely used in data centers, telecommunications infrastructure, enterprise networks, and emerging technologies like 5G and IoT (Internet of Things). The market is driven by the exponential growth in data traffic, increasing demand for high-performance networking solutions, and the need for advanced network security. Leading companies in this space are continuously innovating to offer NPUs with enhanced capabilities, such as higher throughput, lower latency, and greater energy efficiency. As digital transformation accelerates across industries, the NPU market is poised for significant growth, playing a critical role in supporting the infrastructure for cloud computing, AI applications, and connected devices.

Key Functions of NPUs:

Packet Processing: Efficiently handles high volumes of data packets, ensuring minimal latency and high throughput.

Traffic Management: Manages data flow to avoid congestion and optimize network performance.

Deep Packet Inspection (DPI): Analyzes the content of data packets for security, policy enforcement, and quality of service (QoS).

Network Security: Implements advanced security features such as encryption, decryption, and intrusion detection.

Protocol Processing: Supports various network protocols, ensuring compatibility and efficient communication.

Network Processing Unit (NPU) Market Challenges-

1. Technological Complexity

Integration with Existing Systems: Integrating NPUs into existing network architectures and legacy systems can be complex and resource-intensive, requiring significant changes to hardware and software.

Advanced Processing Requirements: As network traffic increases and becomes more complex, NPUs need to continuously evolve to handle higher data rates, advanced protocols, and sophisticated security threats.

2. High Development Costs

R&D Investment: Developing advanced NPUs requires substantial investment in research and development to innovate and keep up with the rapid pace of technological advancements.

Manufacturing Costs: The production of NPUs involves sophisticated manufacturing processes, which can be costly and require specialized facilities.

3. Market Competition

Established Players: The market is dominated by a few large players with significant resources, making it challenging for new entrants to compete.

Alternative Technologies: Competing technologies, such as Field Programmable Gate Arrays (FPGAs) and Graphics Processing Units (GPUs), can also be used for network processing tasks, adding competitive pressure.

4. Scalability Issues

Handling Increased Traffic: As network traffic continues to grow, NPUs must scale effectively to handle higher volumes without compromising performance or efficiency.

Energy Efficiency: Scaling up NPUs while maintaining or improving energy efficiency is a significant challenge, especially as data centers seek to reduce their carbon footprint.

5. Security Concerns

Network Security: NPUs must be capable of handling sophisticated security threats and ensuring robust protection against cyberattacks. Keeping up with the evolving threat landscape is a constant challenge.

Data Privacy: Ensuring data privacy and compliance with regulations such as GDPR and CCPA adds complexity to NPU design and implementation.

6. Standardization and Interoperability

Lack of Standardization: The absence of universal standards for NPU design and functionality can lead to interoperability issues and hinder market growth.

Vendor Lock-In: Proprietary solutions from different vendors can create lock-in scenarios, making it difficult for customers to switch providers or integrate products from multiple vendors.

7. Economic and Market Dynamics

Economic Uncertainty: Fluctuations in the global economy can impact investment in network infrastructure and technology upgrades, affecting NPU demand.

Market Adoption: Convincing network operators and enterprises to adopt NPUs requires demonstrating clear benefits over existing technologies and addressing concerns about ROI.

8. Skilled Workforce

Talent Shortage: Developing and implementing advanced NPUs requires specialized knowledge and skills. There is a shortage of professionals with expertise in this niche area, which can slow down innovation and deployment.

Top Key Players-

MA Lighting

Sandvine

Avolites

Applied Micro Circuits

Alcatel-Lucent

Broadcom

Cisco Systems

Marvell Technology

Ezchip Semiconductor

Qualcomm

Texas Instruments.

More About Report- https://www.credenceresearch.com/report/network-processing-unit-npu-market

Network Processing Unit (NPU) Market Trending Factors-

Rise of Artificial Intelligence and Machine Learning

AI-Driven Networking: The integration of AI and machine learning into networking solutions is increasing the demand for NPUs. These units are capable of handling complex AI-driven tasks such as traffic pattern recognition, anomaly detection, and automated decision-making processes.

Enhanced Performance: AI applications require high-speed data processing and low latency, which NPUs can provide, making them critical for AI-driven network functions.

2. Growth of 5G and IoT

5G Networks: The rollout of 5G networks requires advanced network processing capabilities to manage the increased data traffic and ensure low latency. NPUs are essential for handling the high throughput and dynamic nature of 5G traffic.

IoT Expansion: The proliferation of IoT devices generates vast amounts of data that need to be processed efficiently. NPUs are increasingly used in IoT networks to manage data flow and ensure reliable connectivity.

3. Cloud Computing and Data Centers

Cloud Infrastructure: The growth of cloud services and data centers necessitates robust networking solutions. NPUs play a crucial role in optimizing network performance, managing workloads, and ensuring efficient data routing in cloud environments.

Edge Computing: As edge computing gains traction, NPUs are being deployed to handle data processing closer to the data source, reducing latency and improving real-time data handling capabilities.

4. Network Security and Encryption

Enhanced Security Features: With the increasing sophistication of cyber threats, there is a growing need for NPUs with advanced security features. These include deep packet inspection, intrusion detection, and real-time encryption/decryption capabilities.

Regulatory Compliance: Adherence to data protection regulations such as GDPR and CCPA is driving the adoption of NPUs that can ensure secure and compliant data handling.

5. Software-Defined Networking (SDN) and Network Function Virtualization (NFV)

SDN Integration: NPUs are integral to SDN environments, where they enable dynamic network management, efficient resource allocation, and enhanced network agility.

NFV Adoption: The shift towards NFV is promoting the use of NPUs to virtualize network functions, reducing the need for dedicated hardware and enabling more flexible and scalable network architectures.

6. Energy Efficiency and Sustainability

Green Networking: There is a growing emphasis on energy-efficient networking solutions to reduce the environmental impact of data centers and network infrastructure. NPUs designed for lower power consumption and higher efficiency are gaining traction.

Sustainable Practices: Companies are increasingly adopting sustainable practices, driving demand for NPUs that support energy-saving technologies and contribute to overall sustainability goals.

7. Customization and Flexibility

Programmable NPUs: The trend towards programmable NPUs allows for greater flexibility in handling diverse network tasks and adapting to evolving network requirements. This customization capability is highly valued in dynamic network environments.

Vendor Collaboration: Collaboration between NPU vendors and network equipment manufacturers is leading to more tailored and integrated solutions that address specific network challenges.

8. Increasing Data Traffic and Bandwidth Demand

Data Explosion: The exponential growth of data traffic, driven by video streaming, online gaming, and other bandwidth-intensive applications, is increasing the need for high-performance NPUs to manage this data effectively.

High Bandwidth Applications: Applications requiring high bandwidth, such as virtual reality (VR) and augmented reality (AR), are further driving the demand for advanced NPUs.

Segmentation-

By Product

Wired Network Processing Unit

Wireless Network Processing Unit

By Application

Consumer Electronics

Communications & IT

Military and Government

Others

Browse the full report – https://www.credenceresearch.com/report/network-processing-unit-npu-market

Browse Our Blog: https://www.linkedin.com/pulse/network-processing-unit-npu-market-key-industry-dynamics-analysis-ahopf

Contact Us:

Phone: +91 6232 49 3207

Email: [email protected]

Website: https://www.credenceresearch.com

0 notes