#Testbench

Explore tagged Tumblr posts

Video

youtube

Implement/Add Multiple Time Delays to 1-bit Signals, RTL Code and Testbe...

0 notes

Text

Arduino Simulation vs Bench

I am taking Andre’s “Crash Course Arduino and Microcontroller Development” on Udemy. As a seasoned embedded developer taking this course, I get to commit more details to memory—looking up less—for my own designs. I also use my full lab to enhance the projects during the course. Note the floppy disk connectors used to hook my meters to the breadboard. I learned this trick in Andre’s other course:…

1 note

·

View note

Text

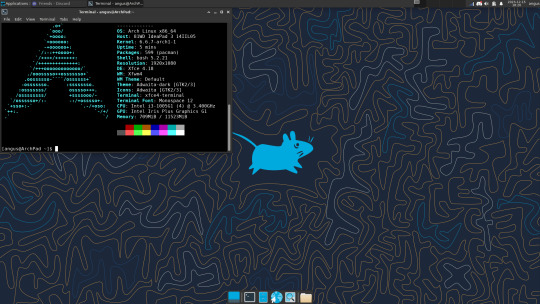

XFCE my beloved

(will post an update on this testbench layout soon)

4 notes

·

View notes

Text

Virtualization in BIOS : Enabled or Disabled? How to Check in Windows 10 / Windows 11

youtube

Subscribe to "Learn And Grow Community"

YouTube : https://www.youtube.com/@LearnAndGrowCommunity

LinkedIn Group : https://www.linkedin.com/groups/7478922/

Blog : https://LearnAndGrowCommunity.blogspot.com/

Facebook : https://www.facebook.com/JoinLearnAndGrowCommunity/

Twitter Handle : https://twitter.com/LNG_Community

DailyMotion : https://www.dailymotion.com/LearnAndGrowCommunity

Instagram Handle : https://www.instagram.com/LearnAndGrowCommunity/

Follow #LearnAndGrowCommunity

Virtualization is a technology that allows a computer to run multiple operating systems at the same time. This is done by creating virtual machines, which are software emulations of physical computers. Virtualization is enabled in the BIOS, which is the basic input/output system.

To check if virtualization is enabled in Windows 10 or Windows 11, you can follow these steps:

Open Command Prompt.

type systeminfo and hit enter.

scroll to the last at Hyper-V requirements :

and check virtualization enabled in firmware : Yes or No.

Another way is -

Open Task Manager.

Click on the "Performance" tab.

Under "CPU," look for the "Virtualization" section.

If the virtualization section says "Enabled,"

If virtualization is not enabled in your BIOS, you may not be able to run certain applications or games. You can enable virtualization in BIOS by following the instructions in your computer's manual. I hope this helps! Thanks for watching! If you found this video helpful, please consider subscribing to @Learnandgrowcomunity for more EdTech tips and tricks.

Subscribe to "Learn And Grow Community"

YouTube : https://www.youtube.com/@LearnAndGrowCommunity LinkedIn Group : https://www.linkedin.com/groups/7478922/

Blog : https://LearnAndGrowCommunity.blogspot.com/

Facebook : https://www.facebook.com/JoinLearnAndGrowCommunity/

Twitter Handle : https://twitter.com/LNG_Community

DailyMotion : https://www.dailymotion.com/LearnAndGrowCommunity Instagram Handle : https://www.instagram.com/LearnAndGrowCommunity/

Follow #LearnAndGrowCommunity

#VHDL #VHDLDesign #BeginnersGuide #DigitalCircuitDesign #LearnVHDL #VHDLTutorial #VHDLBasics #hardwaredesign #FPGA #Verilog HDL #FPGAtools #DesignFlow #XilinxVivado #AlteraQuartusPrime #GHDL #Verilog #DigitalDesign #FPGAoptimization #TimingAnalysis #PhysicalImplementation #FPGAdevelopment #LearnFPGA #VHDLtutorial #FPGAdesignskills #FPGAbeginners #LearnVHDL #Career #Grow #LearnAndGrowCommunity #VHDL #DigitalDesign #HDL #HardwareDescription #LearnVHDL #DigitalCircuits #FSM #Verilog #DesignVerification #VHDL #HardwareDesign #DigitalElectronics #VHDLLanguage #LearnVHDL #VHDLBasics #DigitalDesign #HardwareSimulation #Tips #Tipsandtricks #tricks #Simulation #Synthesis #Xilinx #XilinxVivado #Altera #Quartus #ActiveHDL #ASIC #PlaceandRoute #Tutorial #Learn #Career #SkillUp #HDLDesignLab #DigitalSystemLab #Engineering #TestBench #chip #VLSI #Designing #Programming #Technology #ProgrammingLanguage #EmbeddedSystem #Circuitdesign #VirtualizationInBIOS #EnabledOrDisabled #Windows10 #Windows11 #BIOSConfiguration #VirtualMachines #SoftwareApplications #techtutorials

2 notes

·

View notes

Text

Build a Career in VLSI with RTL Verification and ASIC Design Courses at Takshila Institute

The world of VLSI design is built on strong foundations in RTL (Register Transfer Level) verification and ASIC (Application-Specific Integrated Circuit) design. These two areas are critical to ensuring that semiconductor chips are not only well-designed but also function as intended before fabrication. Takshila Institute of VLSI Technologies in India has emerged as a trusted name, offering advanced training through its RTL verification training institutes and comprehensive ASIC design course online, empowering learners with practical skills for real-world chip development.

Industry-Relevant RTL Verification Training

Takshila Institute of VLSI Technologies offers specialized programs through its RTL verification training institutes aimed at fresh graduates and working professionals. The course focuses on key aspects such as SystemVerilog, UVM (Universal Verification Methodology), functional coverage, assertions, testbench architecture, and simulation-based verification techniques. Students gain hands-on experience using top EDA tools widely adopted in the semiconductor industry. By solving live projects and learning from industry experts, students are trained to identify, debug, and fix design issues at the RTL level effectively.

Learn ASIC Design Anytime with Online Courses

Takshila also provides a well-structured ASIC design course online that caters to learners who prefer flexible and remote learning options. The online course includes modules on RTL design, synthesis, floorplanning, timing analysis, design optimization, and low-power techniques. The course content is delivered through live virtual classes, recorded sessions, interactive labs, and mentor-led projects, ensuring that distance learners receive the same depth and quality as in-classroom students. The course is designed to simulate an actual design environment, preparing students for real-time ASIC development tasks.

Why Choose Takshila Institute of VLSI Technologies?

The success of Takshila Institute of VLSI Technologies lies in its industry-focused curriculum, experienced trainers, modern lab infrastructure, and strong placement support. Whether learning on campus or online, students benefit from continuous mentorship and guidance that goes beyond just completing the course. The institute is known for transforming beginners into skilled VLSI engineers, ready to take on complex verification and ASIC design roles.

Conclusion

If you're looking to start or enhance your career in semiconductor design, Takshila Institute of VLSI Technologies in India provides the perfect platform. With its expert-led RTL verification training institutes and flexible ASIC design course online, Takshila empowers students with the technical expertise and confidence needed to succeed in the competitive VLSI industry.

0 notes

Text

Will AI Eliminate Verification?

A recent blog post looked at the impact artificial intelligence (AI) is having on chip development, focusing on register-transfer-level (RTL) design in general, and the hardware-software interface (HSI) in particular. It seems natural to extend this topic to ask how AI is affecting functional verification of chip designs. Again, there’s plenty of hype on this topic, but it’s important to separate “perhaps someday” visions from the current reality of what AI can accomplish.

AI and IP Verification

The recent post noted that the generation of RTL designs is a domain where AI has shown some success. It used the example of asking ChatGPT to “generate SystemVerilog code for an 8-bit priority encoder” and showed its output. In theory, such generated designs should be “correct by construction” since AI tools are trained on huge datasets that include many successful real-world RTL IP designs. Does this mean that they don’t need to be verified?

The answer, of course, is “no!” since training datasets may include designs with bugs in them, resulting in a large language model (LLM) with errors. In addition, the well documented tendency of AI tools to hallucinate means that the output may sometimes not make sense. It is important to verify any RTL code generated by AI, just as code written by humans. This verification may happen in a standalone IP block testbench, in higher levels of the chip hierarchy, or both.

This leads to the question of whether AI can generate the verification testbench and tests. Typing “generate SystemVerilog UVM testbench and tests for an 8-bit priority encoder” into ChatGPT yields a basic solution that includes a top-level testbench, UVM agent, driver, monitor, and scoreboard, plus a sequence (shown below) with a few common tests. It’s a good start, although an experienced verification engineer would want to add coverage and some additional tests.class priority_encoder_sequence extends uvm_sequence #(priority_encoder_transaction); // Constructor function new(string name = "priority_encoder_sequence"); super.new(name); endfunction // Generate test cases virtual task body(); priority_encoder_transaction tx; // Test case 1: All zeros tx = priority_encoder_transaction::type_id::create("tx"); tx.in_data = 8'b00000000; start_item(tx); finish_item(tx); // Test case 2: Only one bit set tx.in_data = 8'b00000100; start_item(tx); finish_item(tx); // Test case 3: Multiple bits set tx.in_data = 8'b11000000; start_item(tx); finish_item(tx); // Test case 4: All ones tx.in_data = 8'b11111111; start_item(tx); finish_item(tx); endtask endclass

AI and SoC Verification

It seems likely that any AI tool capable of generating an RTL IP block is also capable of generating a standalone testbench and some basic tests. These could also be used to verify a hand-written IP block, or one generated by a different AI tool or LLM. Of course, it is important to verify at least some of the functionality of an IP block once it is instantiated into the chip design. Since AI is not today able to generate the RTL design for a complete chip, it is unreasonable to expect that it could verify one.

Fortunately, there are some aspects of a complex chip that can be verified by current AI tools. The previous post focused on the HSI, which is an essential part of any system on chip (SoC), and on the generation of the memory-mapped, addressable control and status registers (CSRs) that form the hardware side of the HSI. Generating a testbench and tests to verify a CSR block certainly seems within the scope of AI as well.

Thorough hardware-software verification of the HSI involves both the CSR hardware and the low-level software (such as microcode and device drivers) that programs the registers. HSI verification requires tests that exercise the registers and check the results. Many of these tests could potentially be generated by AI tools, although custom sequences that access the registers may be needed. Thus, there must be a way to specify these sequences as well as the set of registers.

Agnisys AI Verification Solutions

The Agnisys IDesignSpec™ Suite is a specification automation solution that generates register RTL code, SystemVerilog Open Verification Methodology (OVM) testbenches and tests, C/C++ tests, and combined hardware-software verification environments. As discussed in the earlier post, the Agnisys SmartDatasheet site uses leading-edge LLM and natural language processing (NLP) technology to interpret natural language datasheets with CSR definitions to generate the RTL code.

IDesignSpec uses the same register definitions, whether from datasheets or from standard formats such as SystemRDL and IP-XACT, to generate verification testbenches and tests. The C/C++ tests can be run on UVM testbenches, co-verification environments, emulators, and even actual chips. The tests are fine-tuned for any special registers specified, including indirect, indexed, read-only/write-only, alias, lock, shadow, interrupt, counter, paged, virtual, external, and read/write pairs.

When custom CSR programming sequences are required, Agnisys provides an AI solution as well. Users can write these sequences in natural language, which is converted via NLP into UVM and C/C++ sequences. Assertions, an important part of RTL verification, can also be specified as statements of design intent in natural language. The Agnisys iSpec.ai site converts these statements into SystemVerilog Assertions (SVA), which could be for the CSRs or any other parts of the design.

Summary

AI is a long way from generating a full-chip testbench and a complete set of tests, but it adds value to the verification flow today for assertions, CSR programming sequences, and HSI testbenches. This frees up a lot of time for the verification engineers, enabling them to focus on more complex chip-level tests. Agnisys is a proven industry leader in using AI for SoC and IP development, with additional capabilities in development.

0 notes

Text

#KeysightTechnologies#Security#cybersecurity#IoT#automotive#industrial#powerelectronics#powermanagement#powersemiconductor

0 notes

Text

CSE231 - Instructions- Solved

There should be ONLY ONE submission per group Submit a .zip named RollNo1_RollNo2.zip file containing code and write-up. The first question requires you to set up your testbench VM. The VM should not require too much resources – approximately 4 GB RAM, with 2 virtual CPU cores and about 20 GB of hard drive space. You need to install Artix-base (runit version) on that following the instructions on…

0 notes

Text

Final project 注意事項

環境: 你的程式必須可以在CAD工作站上進行編譯。 可以使用助教提供的Example進行開發。詳細執行方法請參考資料夾內的README。 Grading: 請注意cout過多information可能會影響你的runtime,請同學將他們盡量註解再繳交。 請參考 /grading 資料夾中的README來測試你的程式。 DEMO時會用相同的script為同學評分,但測試的configuration和testbench會和範��不同。 DEMO…

0 notes

Text

ASIC Verification Training and Online VLSI Verification Courses by Takshila Institute

In the dynamic world of VLSI (Very Large Scale Integration) design, ASIC (Application-Specific Integrated Circuit) verification plays a crucial role in ensuring the functionality, performance, and reliability of complex semiconductor chips. As the semiconductor industry continues to evolve, the demand for skilled ASIC verification professionals is on the rise. Takshila Institute of VLSI Technologies stands as a leading institution offering specialized ASIC verification training in Hyderabad and online VLSI verification courses tailored to meet industry standards.

The ASIC verification training program at Takshila Institute focuses on equipping students with the essential skills required for verifying complex digital designs. The course curriculum covers advanced verification methodologies, including SystemVerilog, UVM (Universal Verification Methodology), functional verification, and testbench architecture. With a hands-on approach, students gain practical experience in creating and debugging test environments, analyzing simulation results, and ensuring design correctness. The institute's state-of-the-art labs and experienced faculty provide an ideal learning environment for mastering ASIC verification.

In addition to on-campus training, Takshila Institute of VLSI Technologies also offers online VLSI verification courses for students and working professionals who seek flexibility in their learning journey. These online courses are designed to cover critical topics such as SystemVerilog basics, UVM concepts, assertion-based verification, and coverage-driven verification. Delivered through live interactive sessions, recorded lectures, and hands-on projects, the online courses ensure that learners gain both theoretical knowledge and practical expertise. The flexible schedule allows participants to balance their professional and academic commitments while advancing their skills.

One of the key strengths of Takshila Institute of VLSI Technologies lies in its industry-oriented curriculum, expert mentors, and strong placement assistance. The institute collaborates with leading semiconductor companies to ensure its training programs align with current industry requirements. Students are encouraged to work on live projects, participate in mock interviews, and gain exposure to real-world ASIC verification challenges.

For aspiring verification engineers, Takshila Institute of VLSI Technologies serves as a reliable platform to build a successful career in ASIC verification and VLSI verification. Whether through on-campus training in Hyderabad or through online VLSI verification courses, the institute remains committed to nurturing talent, fostering innovation, and contributing to the growth of the VLSI industry in India.

0 notes

Video

youtube

CSA Carry Select Adder 8 bit Code with Overflow in Verilog and VHDL with...

0 notes

Text

AXI2OCP Bridge Functional Verification in Bangalore – Inskill Courses

In the rapidly evolving semiconductor and VLSI industry, functional verification is a critical step to ensure robust and reliable designs. The AXI2OCP Bridge Functional Verification process plays a vital role in ensuring seamless protocol conversion between the widely used AXI and OCP protocols. If you’re looking to upskill in this high-demand area, Inskill’s AXI2OCP Bridge Functional Verification course in Bangalore is your ideal choice.

Why AXI2OCP Bridge Verification is Crucial

The AXI2OCP bridge is a vital component in chip design, facilitating communication between AXI and OCP-based systems. Ensuring the functional accuracy of this bridge is critical to avoiding design flaws, which can be costly to rectify. Functional verification using SystemVerilog and UVM methodology helps identify and eliminate potential issues early in the development cycle, saving time and resources.

What Makes Inskill the Best in Bangalore?

Inskill is a premier training institute in Bangalore, known for delivering cutting-edge courses in VLSI and embedded systems. The AXI2OCP Bridge Functional Verification course is designed to provide a comprehensive understanding of:

AXI and OCP protocol basics.

Creating and managing testbenches using SystemVerilog.

Leveraging the UVM methodology for advanced verification.

Real-world application through hands-on projects.

Course Highlights

Expert Guidance: Learn from experienced trainers with years of industry expertise.

Hands-On Projects: Gain practical skills by working on real-world AXI2OCP bridge designs.

Career-Oriented Training: Tailored to meet the current demands of the VLSI and semiconductor industry.

Supportive Environment: Access career guidance, resume building, and interview preparation.

Who Should Enroll?

This course is ideal for engineering students, fresh graduates, and working professionals aiming to specialize in AXI2OCP bridge functional verification or seeking career growth in the VLSI and semiconductor domains.

Why Choose Bangalore for Your Training?

Bangalore, the Silicon Valley of India, is the hub of technology and semiconductor companies. Training in this vibrant city offers unmatched opportunities for networking and career advancement.

Enroll Today!

Take the next step in your career with Inskill’s AXI2OCP Bridge Functional Verification course in Bangalore. Gain in-demand skills, practical experience, and industry connections that will set you apart in the competitive world of VLSI design.

Secure your spot now and unlock your potential with Inskill!

For more information, visit our website or contact us directly. Don’t miss this chance to specialize in AXI2OCP Bridge Functional Verification!

0 notes

Text

VLSI Design And Verification Course For Fresher - VLSI Guru

In the fast-paced world of technology, the VLSI (Very Large Scale Integration) domain stands as a cornerstone for innovations in electronics and semiconductor design. If you’re a fresher aiming to dive into this exciting field, the VLSI Design and Verification Course by VLSI Guru is your perfect launchpad.

Why Choose VLSI as a Career Path?

The demand for skilled professionals in VLSI design and verification is skyrocketing, with industries relying on advanced ASIC (Application-Specific Integrated Circuits) and FPGA (Field-Programmable Gate Arrays) to power cutting-edge technologies. From smartphones to autonomous vehicles, the scope of VLSI is vast and evolving.

What Does the Course Offer?

The VLSI Design and Verification Course by VLSI Guru is tailored for freshers, focusing on:

HDL Languages: Master Verilog and VHDL for RTL coding.

SystemVerilog & UVM: Learn modern verification methodologies for building robust testbenches.

ASIC Design Flow: Gain insights into the complete chip design process.

FPGA Prototyping: Get hands-on experience with FPGA tools and workflows.

Debugging & Tools Expertise: Work with industry-standard tools like Cadence, Synopsys, and Mentor Graphics.

Why VLSI Guru?

VLSI Guru emphasizes practical learning through real-world projects and labs. Freshers are trained to handle challenges in semiconductor design and verification, bridging the gap between academia and industry.

Who Can Enroll?

The course is ideal for engineering graduates in ECE, EE, or CSE with a passion for chip design and a desire to work in leading semiconductor companies.

Start your journey in the semiconductor industry today with VLSI Guru's specialized training.

0 notes

Link

Subscribe to "Learn And Grow Community"

YouTube : https://www.youtube.com/@LearnAndGrowCommunity

LinkedIn Group : https://www.linkedin.com/groups/7478922/

Blog : https://LearnAndGrowCommunity.blogspot.com/

Facebook : https://www.facebook.com/JoinLearnAndGrowCommunity/

Twitter Handle : https://twitter.com/LNG_Community

DailyMotion : https://www.dailymotion.com/LearnAndGrowCommunity

Instagram Handle : https://www.instagram.com/LearnAndGrowCommunity/

Follow #LearnAndGrowCommunity

#VHDL#VHDLDesign#BeginnersGuide#DigitalCircuitDesign#LearnVHDL#VHDLTutorial#VHDLBasics#hardwaredesign#FPGA#VerilogHDL#FPGAtools#DesignFlow#XilinxVivado#AlteraQuartusPrime#GHDL#Verilog#DigitalDesign#TimingAnalysis#FPGAdevelopment#LearnFPGA#FPGAdesignskills#FPGAbeginners#Career#Grow#LearnAndGrowCommunity#HDL#HardwareDescription#FSM#DesignVerification#DigitalElectronics

2 notes

·

View notes

Text

Leading SystemVerilog and Verilog Training Institute in India

In today’s rapidly advancing semiconductor industry, knowledge of hardware description languages like Verilog and SystemVerilog is essential for anyone aiming to build a successful career in VLSI design and verification. Among the institutes offering quality training in this domain, Takshila Institute of VLSI Technologies has emerged as a top destination for professionals and students alike. Renowned for its comprehensive programs, it is widely recognized as one of the best System Verilog training institutes in Hyderabad and a trusted name for those seeking Verilog training institutes in Bangalore.

Takshila Institute of VLSI Technologies offers specialized training programs designed to provide in-depth understanding of Verilog and SystemVerilog, focusing on both RTL design and functional verification. The course begins with the fundamentals of digital design and gradually progresses to advanced topics such as constrained random verification, assertions, coverage analysis, and testbench architecture. This structured approach ensures that learners develop strong coding skills along with practical application in industry-level projects.

As one of the most sought-after SystemVerilog training institutes in Hyderabad, Takshila stands out for its hands-on teaching methodology. Students are trained using real-time projects and industry-standard EDA tools, enabling them to gain practical exposure that goes far beyond textbook learning. The institute's expert faculty, who bring years of industry experience, provide personalized guidance and mentorship throughout the course.

In addition, Takshila Institute is well known among learners seeking Verilog training institutes in Bangalore, thanks to its reputation for delivering high-quality online and hybrid learning options. Students from across the country enroll in its training programs due to the institute’s proven track record of successful placements, strong curriculum, and focus on career readiness.

What makes Takshila unique is its emphasis on both design and verification aspects. Whether you’re a beginner looking to learn Verilog from scratch or an experienced engineer aiming to master SystemVerilog for verification roles, the institute provides a pathway that aligns with individual career goals. Mock interviews, technical assessments, and resume preparation sessions are also part of the course to support students in their job search.

For those aspiring to become skilled VLSI engineers, Takshila Institute of VLSI Technologies offers the perfect blend of theoretical knowledge and practical experience. Recognized among the best SystemVerilog training institutes in Hyderabad and preferred by many searching for Verilog training institutes in Bangalore, Takshila is committed to empowering the next generation of semiconductor professionals with top-tier education and industry-aligned skills.

0 notes

Text

Deep Dive into UVM Register Model- Agnisys, Inc.

UVM Register Model, a key component of the Universal Verification Methodology (UVM), is a standardized methodology for verifying digital designs. UVM Register, a key component of the Universal Verification Methodology (UVM), is a standardized methodology for verifying digital designs. It provides a framework for creating robust and reusable testbenches in the field of hardware verification. One essential aspect of UVM is its Register Abstraction Layer (RAL), which enables efficient verification of register-rich designs. In this article, we’ll take a closer look at the UVM Register Model and explore its key components and concepts.

0 notes