#risc

Explore tagged Tumblr posts

Text

> arm is a Reduced Instruction Set Computer architecture

> look inside

> 200 different instructions just for multiplication

oh ok

17 notes

·

View notes

Text

I absolutely love browsing famous trans women's homemade websites

Wendy Carlos's site is one I can fall down in for hours, and Sophie Wilson's is just delightful.

13 notes

·

View notes

Text

RISC and cëll discuss murder

(audio from getgianni)

60 notes

·

View notes

Text

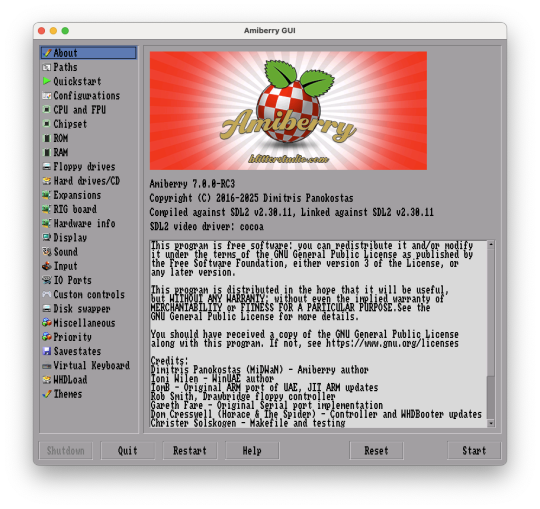

Amiberry v7.0.0-RC3 - A optimized Amiga emulator for Intel/AMD, ARM (32bit and 64bit) and RISC-V platforms

9 notes

·

View notes

Text

Nucleus

Nucleus – a real-time operating system for the embedded systems market from https://archiveos.org/nucleus/

2 notes

·

View notes

Text

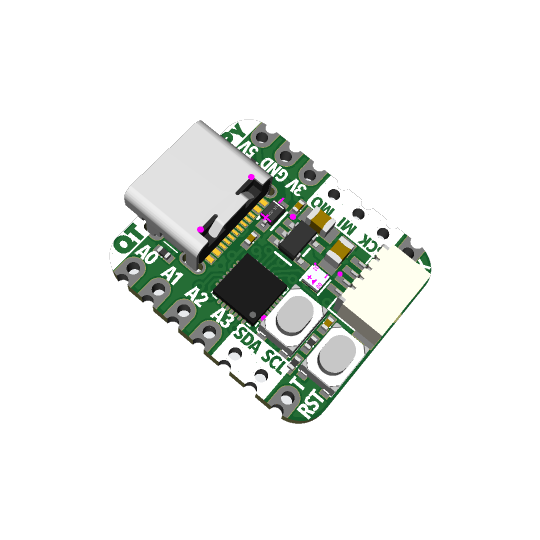

Preview! More RISC-y endeavors with CH32V203

we had so much fun with our CH552 QT Py design, (https://blog.adafruit.com/2024/04/15/desk-of-ladyada-the-8051-throwback-episode-ch552-deskofladyada-adafruit-adafruit/) we thought maybe we could make a board with it's 'big sister' the "35 cent" RISC-V based CH32V203. (https://www.wch-ic.com/products/CH32V203.html). this is the CH32V203G6 which is a QFN-28 version of the chip, with 32KB of Flash and 10KB of SRAM. we would have preferred to use the F8 QFN-20 with double the flash and RAM, but this variant part was easier to buy. we wanted to get going quickly so the board layout is 4-layer. we sorta feel like having a 4-layer board, and the attendant cost, sorta is at odds with such a low cost chip, but we think that converting it to 2-layer would take a couple more hours, and we're getting a bit tired tonight. with UART, SPI, I2C and USB bootloader, we think this is a cute qt for checking out this fun chip.

3 notes

·

View notes

Text

Efemérides Tecnológica: 30 de mayo

John Cocke (1925-2002), nació un día como hoy 30 de mayo. El genio de IBM y "padre del RISC", revolucionó la computación con su visión de procesadores simples y eficientes. ¡Su trabajo en los 70 sentó las bases de la mayoría de nuestros dispositivos actuales! #retrocomputingmx #RISC #johncocke #IBM https://retrocomputingmx.com/o5mb

0 notes

Text

So this next Friday, April 11th 2025, my local gaming group is going to undertake Operation: RISCy Business over at Noble Knight in Fitchburg Wisconsin. A team death match involving the new RISC tech mechs from the recent XTRO.

If you want to drop by the mechs you'll be up against will be the Icarus, Legionnaire, Helios, Battleaxe, Savage Wolf, and Emperor, which will be at 15386 BV at 4/5 skills. The other team will be a team of mechs at the equivalent era and collective BV, although if you have a unit you want to bring to try out, by all means.

1 note

·

View note

Text

Historical Volatility: Ghid Complet pentru Evaluarea Riscului și a Volatilității Pieței

Historical Volatility: Ghid Complet pentru Evaluarea Riscului și a Volatilității Pieței Introducere În lumea tranzacționării, înțelegerea volatilității unui activ este crucială pentru gestionarea riscului și pentru planificarea strategiilor de investiții. Historical Volatility este un indicator tehnic care măsoară variația prețurilor unui activ pe o perioadă specificată, oferind o perspectivă…

#analiza tehnica#strategie de tranzacționare#indicator tehnic#fluctuații preț#Historical Volatility#volatilitate istorică#risc#piață calmă#piață instabilă

0 notes

Text

Limitele plati la termen: indicatori de risc pentru afacerea ta

De cate ori ti s-a intamplat ca unul dintre clienti sa intarzie cu plata facturilor sau solicitarea prelungirii termenelor de plata? Stii de ce au aparut aceste situatii ori ce le-a generat? Ai luat masuri in acest sens pentru a nu te afla din nou in aceasta ipostaza? Este posibil ca firma ta sa ofere produse sau sa presteze servicii cu mult peste capacitatea financiara pe care o poate suporta…

0 notes

Quote

[…] when Sophie Wilson visited WDC in 1983 and saw Mensch and crew laying out the 65816 by hand, it struck her: if this motley crew on a card table could design a CPU, so could Acorn. Thus Wilson and Steve Furber forged their own CPU: the Acorn RISC Machine.

The Apple IIGS Megahertz Myth — Userlandia

0 notes

Note

1 2 and 8 for RISC from the edgy oc asks?

1. What memory would your OC rather just forget?

everything that's ever made them scared. mostly the "bomb implanted in me" bit though

2. What's something about your OC that people wouldn't expect just from looking at them?

they're interested in art and produce it fairly regularly, both procedurally, something analogous to photography, and with their hands, though they tend to prefer drawing things with only straight lines at 90 degree angles.

8. Would your OC ostensibly be able to get away with murder?

no they're stupid and would blow someone's head off in broad daylight and then try to kill everyone who subsequently became an obstacle. subtlety is not a strong suit of theirs

5 notes

·

View notes

Text

Google Wear OS Adopts Qualcomm’s RISC-V Platform

Google’s Wear OS is going to get a new wearable platform powered by Qualcomm’s RISC-V

The first important milestone in the process of bringing RISC-V compliant CPUs to the Ecosystem

In particular:

In order to further their work together on wearables, Qualcomm and Google are building a RISC-V Snapdragon WearTM platform. This platform will provide the power for the next generation of Wear OS solutions.

Work has started, and it will continue, to guarantee that RISC-V applications and a viable software ecosystem will be ready in time for commercial launches of the architecture.

Qualcomm intends to market the RISC-V based wearables solution on a worldwide scale, including in the United States.

Today, Qualcomm Technologies, Inc. made the announcement that they would be expanding their long-standing partnership with Google by providing a RISC-V based wearables solution that can be used in conjunction with Wear OS by Google. This enlarged framework will help pave the way for more goods within the ecosystem to take use of custom CPUs that are low power and high performance.

Specifically, it will help pave the way for more products to take advantage of custom CPUs. The firms will continue to invest in Snapdragon Wear platforms as the top smartwatch chip vendor for the Wear OS ecosystem in the time leading up to this event.

“Qualcomm Technologies have been a foundation of the Wear OS ecosystem, offering high performance, low power solutions for many of our OEM partners,” stated Bjorn Kilburn, the General Manager of Google’s Wear OS division. ” “We are thrilled to deepen our collaboration with Qualcomm Technologies and bring a RISC-V wearable solution to the market,” the company said.

“We are ecstatic to leverage RISC-V and expand our Snapdragon Wear platform as a leading silicon provider for Wear OS,” the company said. “We are a pioneer in this space.” According to Dino Bekis, vice president and general manager of Wearables and Mixed Signal Solutions at Qualcomm Technologies, Inc., “Our Snapdragon Wear platform innovations will help the Wear OS ecosystem rapidly evolve and streamline new device launches globally.”

Both of these firms have joined other industry leaders in launching the RISC-V Software Ecosystem (RISE), and Qualcomm Technologies recently stated that it would invest in a new startup to further the development of RISC-V technology.

RISC-V is an open-source instruction set architecture (ISA), and as such, it allows any firm to design totally unique cores. This stimulates innovation and helps drive the industry forward. This paves the way for other businesses to join the market, which ultimately results in an increase in the amount of innovation and competition.

The openness, flexibility, and scalability provided by RISC-V are all beneficial to the whole value chain, including semiconductor suppliers, original equipment manufacturers (OEMs), end devices, and consumers. The schedule for the introduction of the commercial version of the RISC-V wearable-based solution will be made public at a later time.

Read more on Govindhtech.com

0 notes

Text

Support für teure Apple Watches eingestellt

Apple trifft auch die Reichen und Schönen

Ein "Markenzeichen" von Apple Produkten ist in der öffentlichen Meinung, dass deren Produkte zwar teurer sind als die Konkurrenz, aber dafür bekommt man etwas Solides und auch lebenslangen Support.

Pustekuchen

Dass es sich dabei um Fake News handelt, müssen nun auch die Reichen und Schönen erfahren. Während die nebenstehend abgebildete Uhr noch immer voll funktioniert, gilt das nicht für die $10,000 to $17,000 18-karat gold Apple Watch aus dem Jahr 2015, deren Support mit watchOS 4.3.2 endet. Aber es gibt nicht nur keinen Software Support, sondern auch Ersatzteile werden dafür nicht mehr zur Verfügung gestellt.

Auch wenn wir mit Menschen, die über 10.000€ für eine Armbanduhr ausgeben wenig Mitgefühl entwickeln können, so erinnert uns das Vorgehen des Konzerns an seinen mehr als ruppigen Umgang mit seinen Kunden beim Wechsel der Hardware in den letzten 30 Jahren.

Vom Motorola Chip wechselte Apple in den 90-iger Jahren auf RISC Prozessoren, dann nach der Jahrtausendwende auf Intel und nun produzieren sie eigene Hardware. Jeder dieser Wechsel erzwang bei den Kunden neben dem Kauf der neuen Geräte auch einen kompletten kostenpflichtigen Wechsel der Software.

Innovation als sportliche Übung zum Wohle eines Internetgiganten ...

Mehr dazu bei https://www.theverge.com/2023/10/2/23900158/apple-watch-edition-gold-2015-obsolete-unsupported-beyonce

Kategorie[21]: Unsere Themen in der Presse Short-Link dieser Seite: a-fsa.de/d/3wF Link zu dieser Seite: https://www.aktion-freiheitstattangst.org/de/articles/8550-20231010-support-fuer-teure-apple-watches-eingestellt-.htm

#Apple#SmartWatches#Erstzteile#Hardware#Softwaresupport#lebenslang#Ergonomie#Transparenz#Informationsfreiheit#Motorola#RISC#Intel#Verhaltensänderung#Smartphone#Handy#wearables

1 note

·

View note

Text

RISC OS

RISC OS (Reduced Instrcution Set Computer Operating System) – an OS for desktop computers running ARM processors. RISC OS was originally developed by Acorn Computers Ltd in Cambridge, England has been in continual development since 1989. https://archiveos.org/risc-os/

0 notes