#I3C SLAVE

Explore tagged Tumblr posts

Text

AXI4 Stream DMA IP

Optimize Data Transfer with the AXI4 Stream DMA IP Block Say goodbye to cumbersome data transfer processes and hello to seamless efficiency with our AXI4 Stream DMA IP block! Built to optimize data transfer within your digital system, this lightweight module enables swift and reliable communication between different components. Whether you're working on complex multi-channel audio or video processing, our AXI4 Stream DMA IP block ensures precise and efficient data handling every step of the way. Upgrade your system's performance and enhance your workflow with this high-performance IP block now!

#i3c controller ip#display controller ip#i3c master#lcd controller ip#axi dma scatter gather#i2c controller ip#i2c master ip#espi ip#i2c slave ip#axi dma ip

0 notes

Text

【step by step】Easyi3C Host I3C adapter (1)

Easyi3C is a leading supplier of embedded system tools that simplify the development and debugging of various communication protocols. The company offers a range of products designed to help engineers and developers use I3C/I2C , USB and MIPI, JEDEC, MCTP and other protocols more efficiently.

1. Basic Introduction

Easyi3C Host I3C adapter is a powerful and easy-to-use I3C and I2C host adapter produced by Easyi3C. It connects the computer to the downstream embedded system environment through the USB interface and adopts the advanced I3C and I2C protocol.

Based on the application programming interface (API) function and the Easyi3C Tower console graphical user interface (GUI) tool, combined with the Python development environment, the Easyi3C Host adapter greatly simplifies the development process of I3C/I2C chip testing and data transmission environment. It provides great convenience for AE engineers, FAE engineers, etc. to verify I3C/I2C chips. Simple verification can be done through the graphical console interface, which is easy to use and easy to learn. If you want to test more complex functions or perform automated testing, you can use the rich API functions provided by the manufacturer to quickly implement automated scripts in the Python development environment.

We know that I2C was invented by Philips Semiconductors in 1981, and its history is a bit old and mature. The I3C protocol I3C specification was originally released by in 2017. I3C is the abbreviation of improved internal integrated circuit, which is a 2-wire digital interface similar to I2C. It improves and optimizes the previously released I2C and SPI interfaces, solves the problem of slow I2C communication speed, and optimizes the shortcomings of SPI through four-wire connection. The I3C specification is managed by MIPI Alliance Inc. I3C also solves the problem of high power consumption of I2C. I3C becomes a low-power, low-cost and fast digital interface. It supports multi-point connection between host MCU and peripheral devices such as sensors and multi-master devices. Because the protocol is still very new, there are not many good tools on the market. The series of products launched by Easyi3C will fill this gap. The same interface supports I3C/I2C protocols at the same time, which is convenient for engineers to write automated scripts for chip protocol testing, shorten the product launch cycle, and help the company’s products win the competition.

2. Key features:

Supports MIPI I3C BASIC v1.1 JEDEC JESD403–1 Specifications (JEDEC DDR5 Sideband Bus Spec) I3C Master in SDR mode Variable Working Frequencies (Open-Drain Mode: 1 kHz to 4 MHz (Default: 1MHz); Push-Pull Mode: 100KHz to 12.5 MHz (Default: 4MHz)) Adjustable SCL Duty Cycle Amplitude Variation: 0.8V to 3.3V in steps of 10mV 5ns resolution Supports 7-Bit Slave Addressing Supports Common Command Code (CCC) transactions Supports flexible payload length’s IBI Supports Hot Plug Supports all Dynamic Address Assignments Supports legacy I2C Master, Software configurable I2C pull-up Error Injection such as parity errors USB Type-C port, Max. Current & Voltage: 500 mA @ 5 V Supports online upgrade API support for automation test in Python Physical Size: 114mm x 81mm x 27mm Operating Temperature From –20°C to +85°C

3. Hardware

Accessories:

4. Interface Introduction 4.1 Front Panel

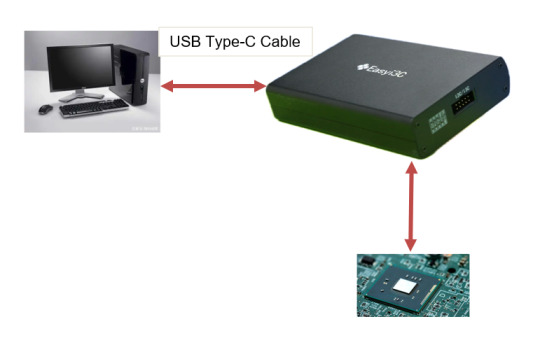

5. Test chip connection method

5.1 Connect the Easyi3C adapter to the I2C/I3C device using a 10-pin cable.

5.2 Connect the Easyi3C adapter to the computer with a USB Type-C cable. The adapter is powered by USB Type-C communication, so no separate external power supply is required, which simplifies device connection.

Next, we will continue to introduce the use of the product in depth.

1 note

·

View note

Text

Basic Understanding of MIPI I3C Protocol

Hello, and welcome to my blog! Today I’m going to share with you some insights on the MIPI I3C protocol, which is a new standard for interconnecting sensors and peripherals in mobile devices. MIPI I3C stands for Mobile Industry Processor Interface — Improved Inter-Integrated Circuit. It is a low-power, high-speed, bi-directional serial bus that supports multiple masters and slaves. It also offers advanced features such as dynamic address assignment, in-band interrupts, hot-join, and command modes. MIPI I3C is designed to be backward compatible with I2C, but with much higher performance and efficiency. It can achieve up to 12.5 Mbps data rate with only two wires: SCL (clock) and SDA (data). It can also support up to 12.7 devices per bus segment, compared to only 112 devices for I2C. MIPI I3C is ideal for connecting sensors such as accelerometers, gyroscopes, magnetometers, pressure sensors, proximity sensors, ambient light sensors, and more. It can also be used for other peripherals such as touch controllers, audio codecs, display controllers, and power management ICs. MIPI I3C is a versatile and powerful protocol that can simplify the design and integration of mobile devices.

If you are interested to understand more about the MIPI I3C Protocol, then you can go through the PiEmbSysTech MIPI I3C Protocol Tutorial Blog. If you have any questions or query, that you need to get answer or you have any idea to share it with the community, you can use Piest Forum.

0 notes

Text

CAN 2.0, LIN 2.2 Controller IP Cores with ASIL B, C, D Packages

T2MIP, the global independent semiconductor IP Cores provider & Technology experts, is pleased to announce the immediate availability its partner’s Automotive Grade Silicon Proven CAN Controller and LIN Controller IP Cores for a niche Automotive and Consumer market. The CAN Controller IP and LIN Controller IP cores are available with ASIL B, ASIL C and ASIL D packages.

The CAN IP cores is a standalone controller for the Controller Area Network (CAN), which is commonly used in automotive and industrial applications. This CAN IP Cores conforms to the Bosch CAN 2.0B specification (2.0B Active) and has a simple CPU interface (8/16/32 bit configurable data width), with little- or big-endian addressing scheme. The CAN supports both standard (11-bit identifier) and extended (29-bit identifier) frames. Hardware message filtering and 64 bytes receive FIFO, enable a back-to-back message reception with a minimum CPU load. The CAN bus uses multi-master bus scheme with one logic bus line and equal node and can support multicasting and broadcasting. Maximum data transfer rate is 1Mbps at maximum 40m bus length when using a twisted wire pair.

The LIN IP cores, is a soft core of the Local Interconnect Network (LIN), this interface is a serial communication protocol, designed primarily to be used in automotive applications. Compared to CAN, LIN is slower, but thanks to its simplicity, is much more cost effective. Our Core is ideal for communication in intelligent sensors and actuators, where the bandwidth and versatility of CAN is not required. The LIN core provides an interface between a microprocessor/microcontroller and a LIN bus. It can work as master or slave LIN node, depending on a work mode, determined by the microprocessor/microcontroller. Our controller supports transmission speed between 1 and 20kb/s, which allows it to transmit and receive LIN messages compatible to LIN 2.2 LIN 2.1 and LIN 1.3

Both the functional safety ISO 26262 and the AEC-Q100 reliability standards have been used to certify these IP Cores. Numerous automotive SoCs and other consumer product clients have used the CAN FD Controller and LIN Controller IP Cores and successfully, efficiently achieved satisfactory results. T2M also boasts the availability of CAN Bus IP Cores and LIN Bus IP Cores certified with ASIL (Automotive Safety Integrity Level) packages with all four safety levels—ASIL A, B, C, and D—where ASIL-D is the most secure and reliable, it follows that it has the most safety-critical procedures and the strictest testing guidelines. The CAN Controller and LIN Controller IP Cores are described at RTL level, allowing target use in FPGA or ASIC technologies.

In addition to CAN Bus and LIN Bus IP Cores, T2M ‘s broad silicon Interface IP Core Portfolio includes many USB, HDMI, Display Port, MIPI (CSI, DSI, UniPro, UFS, RFFE, I3C), PCIe, DDR, 1G Ethernet, V-by-One, programmable SerDes, OnFi and many more available in major Fabs in process geometries as small as 7nm. They can also be ported to other foundries and leading-edge processes nodes on request.

Availability: These Semiconductor Interface IP Cores are available for immediate licensing either stand alone or with pre-integrated Controllers and PHYs. For more information on licensing options and pricing please drop a request / MailTo

About T2M: T2MIP is the global independent semiconductor technology experts, supplying complex semiconductor IP Cores, Software, KGD and disruptive technologies enabling accelerated development of your Wearables, IOT, Communications, Storage, Servers, Networking, TV, STB and Satellite SoCs. For more information, please visit: www.t-2-m.com

0 notes

Text

I3C

mipi Alliance: I3C-Basic špecifikácia: http://resources.mipi.org/mipi-i3c-basic-v1-download MIPI I3C Slave - An NXP Free license MIPI I3C Slave implemented in Verilog for use in FPGAs and Silicon parts: https://github.com/NXP/i3c-slave-design

0 notes

Text

AXI DMA Scatter Gather

Looking to take your digital projects to the next level? Look no further than our amazing Digital Blocks! Say goodbye to the hassle of manual data transfers and hello to the power of AXI DMA Scatter Gather, AXI Stream DMA, and i3C Basic IP. Featuring a user-friendly interface, these blocks are perfect for tech enthusiasts, engineers, and anyone in need of efficient data management. Whether you're a professional or a hobbyist, our Digital Blocks will help you achieve remarkable results. Experience the difference they can make in your projects today!

#i3c controller ip#display controller ip#lcd controller ip#axi dma scatter gather#i2c controller ip#i3c master#i2c master ip#espi ip#i2c slave ip#axi dma ip

0 notes

Text

AXI DMA IP

The AXI DMA IP provides scatter-gather support, which allows the user to specify a list of contiguous buffers and have them distributed across the AXI bus. AXI DMA IP can be configured to handle many tasks concurrently and provide a boost to system performance. Get more details about us from https://www.digitalblocks.com/dma/

#i3c controller ip#display controller ip#lcd controller ip#axi dma scatter gather#i2c controller ip#i2c master ip#espi ip#i3c master#i2c slave ip#axi dma ip

0 notes

Text

AXI DMA Scatter Gather

Looking to elevate your tech setup to the next level? Look no further than our state-of-the-art Digital Blocks! Packed with remarkable features such as AXI DMA scatter gather and AXI Stream DMA, these blocks transform the way you handle data transfers. Say goodbye to slow processing and hello to enhanced performance! Seamlessly manage even the most demanding tasks effortlessly with our Digital Blocks. Upgrade your digital lifestyle today and unlock a world of endless possibilities!

#i3c controller ip#display controller ip#lcd controller ip#axi dma scatter gather#i2c controller ip#espi ip#i2c slave ip#axi dma ip

0 notes

Text

I3C Basic IP

Introducing our amazing Digital blocks! Designed to enhance your electronics projects, these blocks come equipped with advanced features such as the i3C Basic IP, AXI DMA Scatter Gather, and AXI Stream DMA. With i3C Basic IP, you can effortlessly connect and communicate with multiple devices, while the AXI DMA Scatter Gather and AXI Stream DMA enable seamless data transfers and processing. Whether you're a seasoned engineer or an enthusiastic DIYer, our Digital blocks are your perfect go-to solution. Get yours today and take your projects to new heights!

#i3c controller ip#display controller ip#i3c master#lcd controller ip#axi dma scatter gather#i2c controller ip#i2c master ip#espi ip#i2c slave ip#axi dma ip

0 notes

Text

AXI DMA Scatter Gather – What You Need to Know

AXI DMA scatter-gather is a powerful function that allows you to move data between different memory locations in a quick and efficient manner. In this blog post, we will discuss what scatter-gather is and what you need to know about it.

What is AXI DMA scatter-gather?

AXI DMA scatter-gather is a feature that allows a device to send data to multiple memory addresses in a single DMA transaction. This can improve performance by reducing the number of transactions required to send data to multiple destinations.

What are the benefits of using scatter-gather?

There are many benefits to using scatter-gather.

● it allows you to process data more efficiently.

● With scatter-gather, you can process data that is spread out across a network more quickly and easily this makes it a great choice for applications that require a lot of data processing.

● Another benefit of scatter-gather is that it can help improve performance. When data is scattered across a network, it can be accessed more quickly than if it was all stored in one place. This can help improve the performance of applications that rely on data access.

● scatter-gather can also help improve security. When data is scattered across a network, it is more difficult for hackers to access it all at once. This can help keep your data safe from unauthorized access.

How do you use scatter gather?

AXI DMA scatter-gather is a powerful tool that can be used for a variety of purposes.

● In its most basic form, scatter-gather allows you to quickly and easily gather data from multiple sources and combine it into a single dataset. This can be useful for data analysis and reporting, or for creating customizations and extensions for Dynamics 365.

● AXI DMA scatter-gather can also be used to create dynamic lists. This can be useful for creating lists of records that are filtered and sorted based on the user's selections. For example, you could create a list of customers that are located in a specific city, or a list of products that are on sale this week.

● scatter-gather can be used to create lookup tables. This can be useful for creating tables of data that are used to look up information in other tables. For example, you could create a table of states, and then use that table to look up the postal code for a specific state.

#axi dma scatter gather#axi4 dma#axi dma controller#AXI4 DMA controller#Display Controller IP#display controller#LCD Controller IP#I2C controller ip#i2C Master IP#I2C Slave IP#i3C Basic IP#I3C controller ip#i3c master#i3c slave#i3c basic

0 notes

Text

THE IMPORTANCE OF THE AXI INTERCONNECTION INTERFACE

Consider going back in time to the dawn of humanity. When you encounter someone who can't speak or can't understand you, it'll be both frightening and fascinating. Clearly, communication will be impossible unless you discover a way to communicate your separate meanings/intentions in a mutually acceptable manner. In the world of electronics, the same idea applies, as there are numerous sorts of interfaces among electronic equipment. As a result, an uniform communication protocol simplifies data translation in a system, particularly in a System-on-Chip (SoC) system with several systems.

With renowned AMBA Interconnects and standard or bespoke peripheral interfaces, SoC FPGAs such as Digital Blocks provide a versatile CPU programming interface and high-performance transfer rates. With IP releases addressing CPU AXI/AHB backbone DMA Engines, PCI Express DMA, Network Ethernet DMA, and Peripheral high/low data-rate DMA transfers, Digital Blocks DMA Controllers are feature-rich with Multi-Channel, Scatter-Gather functionality. The AXI Master Data Interface spans from 32 to 1024 bits, with configurable data bursts of 1, 4, 8, 16, and up to 16 outstanding read requests, as well as programmable QoS and higher data burst lengths for AXI4 DMA. APB or AXI-lite Slave Interface for CPU access to Control/Status Registers is also provided by the AXI DMA Controller. The DB-DMAC-MC-AXI is optimized for big and small data block transfers as a high-performance DMA Engine.

The AXI Interconnection is the standard language for connecting PS and PL. FPGA companies like Digital Blocks have made it possible to merge software and hardware subsystems on a single chip, and AXI is the primary communication protocol between them. Understanding AXI Interconnections like AXI4 DMA, AXI3, and AHB5 is essential for SoC designers. To know more, visit www.digitalblocks.com

0 notes

Text

I3C SLAVE - THE NEXT GENERATION IP CORE

I3C is a two-wire two-way serial bus that is optimized for several Slave Devices sensor systems and controlled at a time by only a single I3C Master Device. I3C is compatible backward with several Legacy I2C devices, but I3C devices also support significantly higher speeds, new communication modes, and new device roles, with the ability to over time change device roles.

Up to 11 I3 Slave Devices can be supported by an I3C Bus. The maximum number of devices depends on the trace length, the capacitive load per controller, and the device types (I 3C vs I3C), as those factors influence the clock frequency demands. This feature is supported with the MIPI I3C Slave Controller: Using Push-Pull Legacy, two-wire serial interface up to 12.5 MHz Coexistence of I 2C equipment on the same bus (with some limitations) I 2C — like messaging with a single data rate (SDR) Messages mode for HDR-DDR Support for in-band breakage Support Hot-Join Control of time Asynchronous fashion 0 timing 0. Support for synchronous time (not in this release)

SDR Mode is always initialized and mounted on the I3C bus. SDR and HDR-DDR modes are supported by the latest implementation. The LMMI interface issues command to the I3 Slave Controller. The I3C Slave Device Read/Write transactions are decoded from these commands. The I3C Slave Controller can also work in interrupt or polling mode. This means that the LMMI interface can choose whether to poll the I3C Slave for a change in status at regular intervals or wait for the I3C Slave Controller to interrupt it when data needs to be read or written.

An I3C Slave Controller listens for specific I3C Commands sent by the Current Master on the I3C Bus and responds appropriately. All Broadcast Commands, as well as any Directed Commands, addressed directly to the I3C Slave Controller and assisted by that I3C Slave Controller, fall under this category. For more information, click www.digitalblocks.com

0 notes

Text

MORE ABOUT I3C MASTER

The MIPI I3C specification relies on the I2C ecosystem and capabilities while retaining the two-wire serial interface, enable system designers to connect a wider range of sensors to a device while reducing electricity consumption and component and costs of implementation. Moreover, using an I3C master, manufacturers can combine a range of sensors from different suppliers to provide new features while maintaining long battery life and economical systems.

The MIPI I3C specification ensures backward I2C-compatibility and allows for the coexistence of traditional I2C slave devices with the same interface as new MIPI I3C-specification devices. Within the 2-wire interface, the MIPI I3C specification provides band interference, significantly reducing the pin and signal number of the device and permitting the integration of additional sensors within a device. The MIPI I3C master offers higher data performance in comparison with I2C while maintaining low logic complexity using standard I/O pads and providing an accommodating bus topology, making it an attractive option for transition into I3C.

The I3C MIPI specification combines several I2C and SPI functions to provide a uniform standard and scalable interface for the connection of multiple sensors to the soc. It offers a low pin counting and low power solution that provides the necessary output for systems that integrate a large number of sensors and thus lower costs. Applications such as MIPI CSI-2 image-sensors using the CCI have begun to use the I3C to replace the I2C bus that is already existing.

Digital Blocks’ MIPI I3C IP is compatible and easy to integrate into mobile, automotive and IoT SoCs, comply with the MIPI CCI and I2C, and MIPI I3C master specifications. The IP contains in-band interrupts inside the 2-wire interface to provide low pin counts and support operating modes for master and slave systems so that systems with multiple ICs can connect to every sensor efficiently on the single I3C bus. To know more, visit https://www.digitalblocks.com/

0 notes

Photo

I3C Basic - Digital Blocks

The I3c basic is a medium-speed utility and control bus interface used in a variety of mobile, IoT (Internet of Things), and automotive applications to link peripherals to an application processor.For more details https://www.digitalblocks.com/mipi-i3c-ip.html

0 notes

Photo

Display Controller IP

Digital Blocks Display Controller IP Cores can help ASIC/FPGA design teams with system implementations in Medical, Manufacturing, Aerospace/Defense, Automotive, Computer, Monitor, Consumer, AR/VR Headsets, IoT, Wearables, Signage, Gaming, Broadcasting, and Test Instrumentation.For more details just visit at https://www.digitalblocks.com/ip-cores-tft-lcd-display-controller-verilog-ip-core.html

0 notes

Text

BASIC INSIGHTS INTO THE FUTURISTIC AXI PROTOCOL

The AXI protocol was created to meet the interface needs of a wide range of components while allowing for flexibility in how they are connected. It was originally conceived for high-frequency systems. AXI is backward compatible with the AHB and APB from the previous AMBA revision, making it ideal for high-frequency, low-latency designs. Understanding AXI will provide you with a thorough understanding of how an SoC operates, as well as make you a more versatile and well-rounded designer.

The AHB (Advanced High-Performance Bus) is a single-channel bus that allows multiple masters and slaves to communicate. A priority arbiter determines which master gets to use the bus at any given time, while a central decoder selects slaves. Operations are carried out in bursts that can last several bus cycles. An address and control phase precedes the data phase in every burst transfer. AXI4 DMA follows a similar philosophy but employs multiple, dedicated reading and writing channels. AXI, like its predecessor, is burst-based and uses a similar address and control phase prior to data exchange. Out-of-order transactions, unaligned data transfers, cache support signals, and a low-power interface are among the new features in AXI.

Between an AXI master and a slave, there are five distinct outlets. They are the following::

● Read address channel

● Read data channel

● Write address channel

● Write data channel

● Write response channel

Interconnects, in reality, include slave interfaces that connect to AXI masters and master interfaces that connect to AXI slaves. The implementation determines how different masters communicate with different slaves in an interconnect. A shared address bus, shared data bus, both shared, or neither shared interconnect can be used. In modern SoC design, AXI4 DMA has become a popular protocol. Simpler bus protocols like Avalon and Wishbone will be much easier to learn once you've mastered AXI. To have access to this marvel techno core, pay a visit to https://www.digitalblocks.com

0 notes