#i3c basic

Explore tagged Tumblr posts

Text

How i2C protocol works....

#mobicationhub #mobicationhub9509959090 #Protocol #reelsfypシ #i2c #institute #phonerepair #mobilerepaircoursejaipur #mobilerepairing #working #1monthcours #laptop

#i2c protocol#i2c protocol tutorial#protocol#spi protocol#communication protocols#i2c protocol vs spi protocol#communication protocol#how i2c protocol works#i2c protocol - inter integrated circuit protocol#i2c communication protocol#i2c protocol working#serial communication protocol#inter integrated circuit protocol#inter-integrated circuit protocol#i2c bus protocol#i3c protocol#what is i2c protocol#basics of i2c protocol#spi protocol tutorial

0 notes

Text

"Accelerating System Performance with AXI4 Stream DMA, AXI Stream DMA, and eSPI IP Digital Blocks"

Digital blocks play a crucial role in modern electronic systems, providing essential functionality for communication, data transfer, and control. Among these blocks, the AXI4 Stream DMA, AXI Stream DMA, and eSPI IP are three critical components that enable efficient data transfer and communication between different modules in a system. In this blog, we will explore these digital blocks and their features, applications, and benefits.

AXI4 Stream DMA: The AXI4 Stream Direct Memory Access (DMA) is a digital block that facilitates high-speed data transfer between different modules in a system. It is a flexible and scalable interface that allows the transfer of large amounts of data between a source and a destination without involving the CPU. The AXI4 Stream DMA block is designed to be integrated into an AXI4-based system and supports a wide range of data transfer modes and burst sizes.

One of the main advantages of using the AXI4 Stream DMA block is its ability to offload data transfer tasks from the CPU, thereby reducing the workload on the processor and improving system performance. This makes it ideal for applications that require high-speed data transfer, such as video processing, audio processing, and network data transfer.

AXI Stream DMA: Similar to the AXI4 Stream DMA, the AXI Stream DMA is a digital block that provides a high-bandwidth, low-latency interface for data transfer in an AXI-based system. The AXI Stream DMA block is optimized for streaming data transfer and is ideal for applications that require real-time data transfer, such as audio and video processing, image processing, and machine learning.

One of the key features of the AXI Stream DMA block is its support for multiple channels, which enables simultaneous data transfer between different modules in a system. This feature makes it ideal for applications that require parallel data transfer, such as multi-camera video processing and multi-channel audio processing.

eSPI IP: The Enhanced Serial Peripheral Interface (eSPI) is a digital block that provides a high-speed, low-latency interface for communication between different modules in a system. The eSPI IP block is designed to replace the legacy Low Pin Count (LPC) interface and improve system performance by providing faster data transfer rates, higher bandwidth, and improved scalability.

One of the key features of the eSPI IP block is its support for multiple devices, which enables communication between different modules in a system, such as the CPU, chipset, and peripherals. This feature makes it ideal for applications that require efficient communication between multiple devices, such as server systems, high-performance computing systems, and embedded systems.

In conclusion, the AXI4 Stream DMA, AXI Stream DMA, and eSPI IP are three critical digital blocks that enable efficient data transfer and communication between different modules in a system. These blocks are designed to improve system performance, reduce CPU workload, and enable real-time data transfer and communication. As digital systems continue to evolve, these blocks will play an increasingly important role in enabling faster, more efficient, and more scalable systems.

0 notes

Text

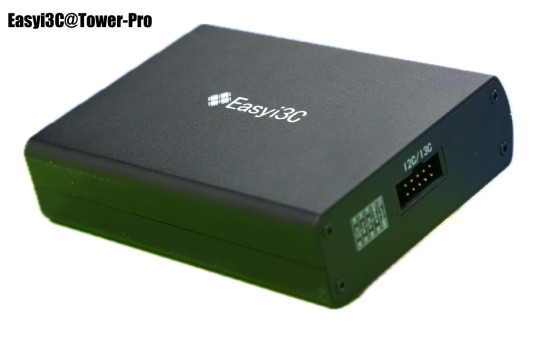

【step by step】Easyi3C Host I3C adapter (1)

Easyi3C is a leading supplier of embedded system tools that simplify the development and debugging of various communication protocols. The company offers a range of products designed to help engineers and developers use I3C/I2C , USB and MIPI, JEDEC, MCTP and other protocols more efficiently.

1. Basic Introduction

Easyi3C Host I3C adapter is a powerful and easy-to-use I3C and I2C host adapter produced by Easyi3C. It connects the computer to the downstream embedded system environment through the USB interface and adopts the advanced I3C and I2C protocol.

Based on the application programming interface (API) function and the Easyi3C Tower console graphical user interface (GUI) tool, combined with the Python development environment, the Easyi3C Host adapter greatly simplifies the development process of I3C/I2C chip testing and data transmission environment. It provides great convenience for AE engineers, FAE engineers, etc. to verify I3C/I2C chips. Simple verification can be done through the graphical console interface, which is easy to use and easy to learn. If you want to test more complex functions or perform automated testing, you can use the rich API functions provided by the manufacturer to quickly implement automated scripts in the Python development environment.

We know that I2C was invented by Philips Semiconductors in 1981, and its history is a bit old and mature. The I3C protocol I3C specification was originally released by in 2017. I3C is the abbreviation of improved internal integrated circuit, which is a 2-wire digital interface similar to I2C. It improves and optimizes the previously released I2C and SPI interfaces, solves the problem of slow I2C communication speed, and optimizes the shortcomings of SPI through four-wire connection. The I3C specification is managed by MIPI Alliance Inc. I3C also solves the problem of high power consumption of I2C. I3C becomes a low-power, low-cost and fast digital interface. It supports multi-point connection between host MCU and peripheral devices such as sensors and multi-master devices. Because the protocol is still very new, there are not many good tools on the market. The series of products launched by Easyi3C will fill this gap. The same interface supports I3C/I2C protocols at the same time, which is convenient for engineers to write automated scripts for chip protocol testing, shorten the product launch cycle, and help the company’s products win the competition.

2. Key features:

Supports MIPI I3C BASIC v1.1 JEDEC JESD403–1 Specifications (JEDEC DDR5 Sideband Bus Spec) I3C Master in SDR mode Variable Working Frequencies (Open-Drain Mode: 1 kHz to 4 MHz (Default: 1MHz); Push-Pull Mode: 100KHz to 12.5 MHz (Default: 4MHz)) Adjustable SCL Duty Cycle Amplitude Variation: 0.8V to 3.3V in steps of 10mV 5ns resolution Supports 7-Bit Slave Addressing Supports Common Command Code (CCC) transactions Supports flexible payload length’s IBI Supports Hot Plug Supports all Dynamic Address Assignments Supports legacy I2C Master, Software configurable I2C pull-up Error Injection such as parity errors USB Type-C port, Max. Current & Voltage: 500 mA @ 5 V Supports online upgrade API support for automation test in Python Physical Size: 114mm x 81mm x 27mm Operating Temperature From –20°C to +85°C

3. Hardware

Accessories:

4. Interface Introduction 4.1 Front Panel

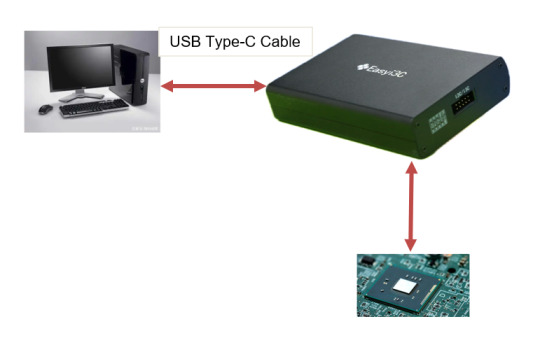

5. Test chip connection method

5.1 Connect the Easyi3C adapter to the I2C/I3C device using a 10-pin cable.

5.2 Connect the Easyi3C adapter to the computer with a USB Type-C cable. The adapter is powered by USB Type-C communication, so no separate external power supply is required, which simplifies device connection.

Next, we will continue to introduce the use of the product in depth.

1 note

·

View note

Text

Basic Understanding of MIPI I3C Protocol

Hello, and welcome to my blog! Today I’m going to share with you some insights on the MIPI I3C protocol, which is a new standard for interconnecting sensors and peripherals in mobile devices. MIPI I3C stands for Mobile Industry Processor Interface — Improved Inter-Integrated Circuit. It is a low-power, high-speed, bi-directional serial bus that supports multiple masters and slaves. It also offers advanced features such as dynamic address assignment, in-band interrupts, hot-join, and command modes. MIPI I3C is designed to be backward compatible with I2C, but with much higher performance and efficiency. It can achieve up to 12.5 Mbps data rate with only two wires: SCL (clock) and SDA (data). It can also support up to 12.7 devices per bus segment, compared to only 112 devices for I2C. MIPI I3C is ideal for connecting sensors such as accelerometers, gyroscopes, magnetometers, pressure sensors, proximity sensors, ambient light sensors, and more. It can also be used for other peripherals such as touch controllers, audio codecs, display controllers, and power management ICs. MIPI I3C is a versatile and powerful protocol that can simplify the design and integration of mobile devices.

If you are interested to understand more about the MIPI I3C Protocol, then you can go through the PiEmbSysTech MIPI I3C Protocol Tutorial Blog. If you have any questions or query, that you need to get answer or you have any idea to share it with the community, you can use Piest Forum.

0 notes

Text

ETSI adopts of MIPI I3C Basic into ETSI Smart Secure Platform

ETSI adopts of MIPI I3C Basic into ETSI Smart Secure Platform

The MIPI Alliance, an international organization that develops interface specifications for mobile and mobile-influenced industries, and ETSI Technical Committee Secure Element Technologies (TC SET) announced the adoption of the I3C Interface for SSP (TS 103 818) specification, allowing the MIPI I3C Basicspecification to serve as a physical and logical link layer for the ETSI Smart Secure…

View On WordPress

0 notes

Text

Complete UFS 3.1 Controller IP Cores Solution

T2MIP, the global independent semiconductor IP Cores provider & Technology experts, is pleased to announce the licensing of its partner’s JEDEC compliant and Silicon proven Total UFS Solution with the UFS v3.1 Host Controller IP Cores, MIPI M-PHY v4.1 IP Cores and the MIPI UniPro v1.8 IP Cores to a Tier-1 Chinese Company for their UFS Device application to maximize processing speed of high-density flash data storage.

The Complete UFS 3 Solution comes as a packaged bundle with total UFS Device functionality which includes M-PHY, Unipro, and UFS Controller IP Cores along with smaller blocks integrated together making for a complex yet a highly modular design. These smaller blocks include F-PHY, Voltage Regulator, Voltage Detector, Oscillator, Thermal Sensor, Noise Generator, GPIO and Power Switch helps to maintain and also performs interface management and power management /control processes which simplifies its implementation and integration into the chip.

The most important part of the solution, UFS v3.1 Host Controller IP Cores is a UFS synchronous serial interface designed for use in applications where power consumption needs to be curtailed, with its most basic usage, being to help communicate between host processor and mass storage devices like flash and other non-volatile memories. This communication is achieved via UFS Device, using MIPI UniPro as Link and MPHY for PHY layers. The UFS follows the common methods used for specifying the location of blocks of data stored on computer storage devices with the help of TAG overlap/LBA overlap. Its structured and synchronous design allows for a full range of UPIU packets Data In & Data Out.

MIPI M-PHY and MIPI Unipro Controller IP Cores were licensed as an integral part of the total UFS solution for a lossless and high-density Flash storage. The MIPI M-PHY v4.1 IP Cores is a serial interface technology with high bandwidth capabilities and supports HS Gear4 rates up to 11.6Gbps, which is particularly developed for mobile applications to obtain low pin count combined with very good power efficiency. The MIPI Unipro v1.8 Controller IP Cores provides the capability to control the UniPro link over a MIPI M-PHY link. It is a high-performance, chip-to-chip, serial interconnect bus for mobile applications boasting a Maximum R/W Performance up to 2170MB/s.

The UFS Host Controller IP cores along with the MIPI M-PHY IP Cores and MIPI UniPro Controller IP Cores have also been used in semiconductor industry’s Enterprise Computing, Storage area networks, Wireless and mobile devices, IoT, Embedded systems and other Consumer Electronics…

In addition to UFS, M-PHY and Unipro IP Cores, T2M ‘s broad silicon Interface IP Core Portfolio includes USB, HDMI, Display Port, DDR, MIPI (CSI, DSI, Soundwire, I3C), PCIe, 10/100/1000 Ethernet, V by One, programmable SerDes, SD/eMMCs and many more, available in major Fabs in process geometries as small as 7nm. They can also be ported to other foundries and leading-edge processes nodes on request.

Availability: These Semiconductor Interface IP Cores are available for immediate licensing either stand alone or with pre-integrated Controllers and PHYs. For more information on licensing options and pricing please drop a request / MailTo

About T2M: T2MIP is the global independent semiconductor technology experts, supplying complex semiconductor IP Cores, Software, KGD and disruptive technologies enabling accelerated development of your Wearables, IOT, Communications, Storage, Servers, Networking, TV, STB and Satellite SoCs. For more information, please visit: www.t-2-m.com

1 note

·

View note

Text

New Precision Temperature Sensor Comes with Two-Wire Bus Serial Interface

Enables memory modules and temperature-sensitive systems with real-time, closed-loop thermal management algorithms Supports I²C, SMBUS and I3C Basic protocol for data rates up to 12.5 MHz Features in-band interrupts, parity check, and packet error checks This story is related to the following: HVAC Test & Measuring Instruments Search for suppliers of: Temperature Sensors from HVAC /fullstory/new-precision-temperature-sensor-comes-with-two-wire-bus-serial-interface-40035739 via http://www.rssmix.com/

0 notes

Text

New Precision Temperature Sensor Comes with Two-Wire Bus Serial Interface

Enables memory modules and temperature-sensitive systems with real-time, closed-loop thermal management algorithms Supports I²C, SMBUS and I3C Basic protocol for data rates up to 12.5 MHz Features in-band interrupts, parity check, and packet error checks This story is related to the following: HVAC Test & Measuring Instruments Search for suppliers of: Temperature Sensors from Air Conditioning /fullstory/new-precision-temperature-sensor-comes-with-two-wire-bus-serial-interface-40035739 via http://www.rssmix.com/

0 notes

Link

Diet is a modifiable factor associated with the risk of several cancers, with convincing evidence showing a link between diet and breast cancer. The role of cruciferous vegetables, is an active area of research in cancer chemoprevention. A recent study focused on 3,3′-diindolylmethane (DIM), the major bioactive indole in crucifers. Research of the cancer-preventive activity of DIM has revealed basic mechanistic, animal, and human trial data. Bioactive DIM has demonstrated chemopreventive activity in all stages of breast cancer carcinogenesis. The review described current evidence related to the metabolism and mechanisms of DIM involved in the prevention of breast cancer.

EstroDIM is a targeted supplement that combines the synergistic benefits of the cruciferous vegetable metabolites Indole-3-carbinol (I3C) and diindolylmethane (DIM) to support proper estrogen metabolism. Formulating I3C and DIM together creates the ideal combination of beneficial metabolites that work together to support estrogen balance, breast and prostate health.

The Health Benefits of Cruciferous Vegetable Metabolites

Many of the health benefits derived from eating cruciferous vegetables (cabbage, brussels sprouts, broccoli, etc.), especially those shown to be beneficial for breast and prostate health, are thought to be derived from the group of secondary metabolites known as glucosinolates. When these vegetables are cut, crushed or chewed, the actions of the enzyme myrosinase (released from the cells) hydrolyses these glucosinolates into other compounds. For instance, glucosinolates from broccoli and brussel sprouts readily convert into I3C when consumed. I3C can then be further converted via stomach acid into other health promoting compounds, including DIM. These compounds have generally been thought to be responsible for the various cellular activities that lead to hormone health.

Overview

Estrogen collectively refers to the female hormones estradiol, estrone and estriol. Hormones have important functions in every area of the body. They are chemical messengers that interact with cells all over the body (especially tissues that are more sensitive to them, including breast and prostate tissues.). The most important message they deliver is to grow, divide, and multiply. For this reason, hormones are critically important in human development and tissue repair. Supporting proper estrogen synthesis, metabolism and detoxification is essential for proper hormonal balance. Depending on how estrogen is metabolized it can result in different metabolites, each with individual biological activity. By keeping hormones in balance and ensuring the body is able to process hormones properly, cruciferous vegetable metabolites (such as I3C and DIM) work together to reduce hormone overload and maintain cellular health. Current data on I3C and DIM, suggests that these phytonutrients have strong potential for supporting breast, cervical, uterine and prostate health.1-4 I3C is a naturally occurring compound derived from cruciferous vegetables such as broccoli, brussel sprouts and cabbage. Together, I3C and DIM promote the creation of the more favorable and protective 2-hydroxyestrone (2-OHE) metabolite versus production of 4-hydroxyestrone (4-OHE) and 16-alpha-hydroxyestrone (16-alphaOHE), metabolites which can overstimulate cells and create free radicals that cause DNA damage.5 The influence of I3C and DIM on estrogen metabolism creates a more desirable ratio of 2-OHE to 16-alpha-OHE. This assessment of 2:16 alpha- OHE ratio has been used to evaluate breast health. With this in mind, EstroDIM includes targeted doses of both I3C and DIM in one capsule a day dosing to make daily balancing of hormones easy and convenient.

I3C

Indole-3-carbinol (I3C) is a naturally occurring compound found in numerous cruciferous vegetables, such as broccoli, cauliflower, kale and cabbage. Following ingestion of I3C, the body converts it to several different metabolites, one of which is diindolylmethane (DIM). Both of these compounds, as well as many other I3C metabolites, have been shown to impact metabolic shifts and cellular activities for improved health outcomes. I3C has also been shown to temper estrogen signals by competing for binding sites and inhibiting the activity of estrogen receptors.6-15 A study published in the Journal of Nutrition unveiled evidence that I3C supports healthy cellular function related to estrogen metabolism.16

DIM

Diindolylmethane (DIM) is a phytonutrient and plant indole also found in cruciferous vegetables with potential for enhancing proliferation of healthy cells and cellular activities. As a dimer (formed chemical structure of two substances) of indole-3-carbinol, diindolylmethane (DIM) promotes beneficial estrogen metabolism in both sexes supporting the formation of healthy estrogen metabolites and enhancing the potential for greater antioxidant activity.17-19

Dr. Kevin Conners, D.PSc., FICT, FAARFM

Dr. Conners graduated with his doctorate from Northwestern Health Sciences University in 1986 and has been studying alternative cancer care for over 20 years. He holds AMA Fellowships in Regenerative & Functional Medicine and Integrative Cancer Therapy.

He is the author of numerous books including, Stop Fighting Cancer and Start Treating the Cause, Cancer Can’t Kill You if You’re Already Dead, Help, My Body is Killing Me, Chronic Lyme, 3 Phases of Lyme, 23 Steps to Freedom, and many more you can download for FREE on our books page.

via News

0 notes

Text

I3C

mipi Alliance: I3C-Basic špecifikácia: http://resources.mipi.org/mipi-i3c-basic-v1-download MIPI I3C Slave - An NXP Free license MIPI I3C Slave implemented in Verilog for use in FPGAs and Silicon parts: https://github.com/NXP/i3c-slave-design

0 notes

Text

AXI DMA Scatter Gather

Looking to take your digital projects to the next level? Look no further than our amazing Digital Blocks! Say goodbye to the hassle of manual data transfers and hello to the power of AXI DMA Scatter Gather, AXI Stream DMA, and i3C Basic IP. Featuring a user-friendly interface, these blocks are perfect for tech enthusiasts, engineers, and anyone in need of efficient data management. Whether you're a professional or a hobbyist, our Digital Blocks will help you achieve remarkable results. Experience the difference they can make in your projects today!

#i3c controller ip#display controller ip#lcd controller ip#axi dma scatter gather#i2c controller ip#i3c master#i2c master ip#espi ip#i2c slave ip#axi dma ip

0 notes

Text

I3C Basic IP

Introducing our amazing Digital blocks! Designed to enhance your electronics projects, these blocks come equipped with advanced features such as the i3C Basic IP, AXI DMA Scatter Gather, and AXI Stream DMA. With i3C Basic IP, you can effortlessly connect and communicate with multiple devices, while the AXI DMA Scatter Gather and AXI Stream DMA enable seamless data transfers and processing. Whether you're a seasoned engineer or an enthusiastic DIYer, our Digital blocks are your perfect go-to solution. Get yours today and take your projects to new heights!

#i3c controller ip#display controller ip#i3c master#lcd controller ip#axi dma scatter gather#i2c controller ip#i2c master ip#espi ip#i2c slave ip#axi dma ip

0 notes

Text

AXI DMA Scatter Gather – What You Need to Know

AXI DMA scatter-gather is a powerful function that allows you to move data between different memory locations in a quick and efficient manner. In this blog post, we will discuss what scatter-gather is and what you need to know about it.

What is AXI DMA scatter-gather?

AXI DMA scatter-gather is a feature that allows a device to send data to multiple memory addresses in a single DMA transaction. This can improve performance by reducing the number of transactions required to send data to multiple destinations.

What are the benefits of using scatter-gather?

There are many benefits to using scatter-gather.

● it allows you to process data more efficiently.

● With scatter-gather, you can process data that is spread out across a network more quickly and easily this makes it a great choice for applications that require a lot of data processing.

● Another benefit of scatter-gather is that it can help improve performance. When data is scattered across a network, it can be accessed more quickly than if it was all stored in one place. This can help improve the performance of applications that rely on data access.

● scatter-gather can also help improve security. When data is scattered across a network, it is more difficult for hackers to access it all at once. This can help keep your data safe from unauthorized access.

How do you use scatter gather?

AXI DMA scatter-gather is a powerful tool that can be used for a variety of purposes.

● In its most basic form, scatter-gather allows you to quickly and easily gather data from multiple sources and combine it into a single dataset. This can be useful for data analysis and reporting, or for creating customizations and extensions for Dynamics 365.

● AXI DMA scatter-gather can also be used to create dynamic lists. This can be useful for creating lists of records that are filtered and sorted based on the user's selections. For example, you could create a list of customers that are located in a specific city, or a list of products that are on sale this week.

● scatter-gather can be used to create lookup tables. This can be useful for creating tables of data that are used to look up information in other tables. For example, you could create a table of states, and then use that table to look up the postal code for a specific state.

#axi dma scatter gather#axi4 dma#axi dma controller#AXI4 DMA controller#Display Controller IP#display controller#LCD Controller IP#I2C controller ip#i2C Master IP#I2C Slave IP#i3C Basic IP#I3C controller ip#i3c master#i3c slave#i3c basic

0 notes

Text

THE IMPORTANCE OF THE AXI INTERCONNECTION INTERFACE

Consider going back in time to the dawn of humanity. When you encounter someone who can't speak or can't understand you, it'll be both frightening and fascinating. Clearly, communication will be impossible unless you discover a way to communicate your separate meanings/intentions in a mutually acceptable manner. In the world of electronics, the same idea applies, as there are numerous sorts of interfaces among electronic equipment. As a result, an uniform communication protocol simplifies data translation in a system, particularly in a System-on-Chip (SoC) system with several systems.

With renowned AMBA Interconnects and standard or bespoke peripheral interfaces, SoC FPGAs such as Digital Blocks provide a versatile CPU programming interface and high-performance transfer rates. With IP releases addressing CPU AXI/AHB backbone DMA Engines, PCI Express DMA, Network Ethernet DMA, and Peripheral high/low data-rate DMA transfers, Digital Blocks DMA Controllers are feature-rich with Multi-Channel, Scatter-Gather functionality. The AXI Master Data Interface spans from 32 to 1024 bits, with configurable data bursts of 1, 4, 8, 16, and up to 16 outstanding read requests, as well as programmable QoS and higher data burst lengths for AXI4 DMA. APB or AXI-lite Slave Interface for CPU access to Control/Status Registers is also provided by the AXI DMA Controller. The DB-DMAC-MC-AXI is optimized for big and small data block transfers as a high-performance DMA Engine.

The AXI Interconnection is the standard language for connecting PS and PL. FPGA companies like Digital Blocks have made it possible to merge software and hardware subsystems on a single chip, and AXI is the primary communication protocol between them. Understanding AXI Interconnections like AXI4 DMA, AXI3, and AHB5 is essential for SoC designers. To know more, visit www.digitalblocks.com

0 notes

Text

I3C SLAVE - THE NEXT GENERATION IP CORE

I3C is a two-wire two-way serial bus that is optimized for several Slave Devices sensor systems and controlled at a time by only a single I3C Master Device. I3C is compatible backward with several Legacy I2C devices, but I3C devices also support significantly higher speeds, new communication modes, and new device roles, with the ability to over time change device roles.

Up to 11 I3 Slave Devices can be supported by an I3C Bus. The maximum number of devices depends on the trace length, the capacitive load per controller, and the device types (I 3C vs I3C), as those factors influence the clock frequency demands. This feature is supported with the MIPI I3C Slave Controller: Using Push-Pull Legacy, two-wire serial interface up to 12.5 MHz Coexistence of I 2C equipment on the same bus (with some limitations) I 2C — like messaging with a single data rate (SDR) Messages mode for HDR-DDR Support for in-band breakage Support Hot-Join Control of time Asynchronous fashion 0 timing 0. Support for synchronous time (not in this release)

SDR Mode is always initialized and mounted on the I3C bus. SDR and HDR-DDR modes are supported by the latest implementation. The LMMI interface issues command to the I3 Slave Controller. The I3C Slave Device Read/Write transactions are decoded from these commands. The I3C Slave Controller can also work in interrupt or polling mode. This means that the LMMI interface can choose whether to poll the I3C Slave for a change in status at regular intervals or wait for the I3C Slave Controller to interrupt it when data needs to be read or written.

An I3C Slave Controller listens for specific I3C Commands sent by the Current Master on the I3C Bus and responds appropriately. All Broadcast Commands, as well as any Directed Commands, addressed directly to the I3C Slave Controller and assisted by that I3C Slave Controller, fall under this category. For more information, click www.digitalblocks.com

0 notes

Text

MORE ABOUT I3C MASTER

The MIPI I3C specification relies on the I2C ecosystem and capabilities while retaining the two-wire serial interface, enable system designers to connect a wider range of sensors to a device while reducing electricity consumption and component and costs of implementation. Moreover, using an I3C master, manufacturers can combine a range of sensors from different suppliers to provide new features while maintaining long battery life and economical systems.

The MIPI I3C specification ensures backward I2C-compatibility and allows for the coexistence of traditional I2C slave devices with the same interface as new MIPI I3C-specification devices. Within the 2-wire interface, the MIPI I3C specification provides band interference, significantly reducing the pin and signal number of the device and permitting the integration of additional sensors within a device. The MIPI I3C master offers higher data performance in comparison with I2C while maintaining low logic complexity using standard I/O pads and providing an accommodating bus topology, making it an attractive option for transition into I3C.

The I3C MIPI specification combines several I2C and SPI functions to provide a uniform standard and scalable interface for the connection of multiple sensors to the soc. It offers a low pin counting and low power solution that provides the necessary output for systems that integrate a large number of sensors and thus lower costs. Applications such as MIPI CSI-2 image-sensors using the CCI have begun to use the I3C to replace the I2C bus that is already existing.

Digital Blocks’ MIPI I3C IP is compatible and easy to integrate into mobile, automotive and IoT SoCs, comply with the MIPI CCI and I2C, and MIPI I3C master specifications. The IP contains in-band interrupts inside the 2-wire interface to provide low pin counts and support operating modes for master and slave systems so that systems with multiple ICs can connect to every sensor efficiently on the single I3C bus. To know more, visit https://www.digitalblocks.com/

0 notes