#VHDL examples

Explore tagged Tumblr posts

Text

youtube

Insights Sequential and Concurrent Statements - No More Confusion [Beginner’s Guide] - Part ii

Subscribe to "Learn And Grow Community"

YouTube : https://www.youtube.com/@LearnAndGrowCommunity

LinkedIn Group : https://www.linkedin.com/groups/7478922/

Blog : https://LearnAndGrowCommunity.blogspot.com/

Facebook : https://www.facebook.com/JoinLearnAndGrowCommunity/

Twitter Handle : https://twitter.com/LNG_Community

DailyMotion : https://www.dailymotion.com/LearnAndGrowCommunity

Instagram Handle : https://www.instagram.com/LearnAndGrowCommunity/

Follow #LearnAndGrowCommunity

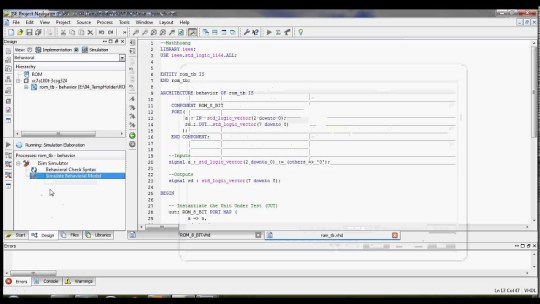

This is the Part ii of last Video "VHDL Basics : Insights Sequential and Concurrent Statements - No More Confusion [Beginner’s Guide]", for deeper understanding, and it is very important to have deeper insights on Sequential and Concurrent statement, if you are designing anything in VHDL or Verilog HDL. In this comprehensive tutorial, we will cover everything you need to know about VHDL sequential and concurrent statements. Sequential statements allow us to execute code in a step-by-step manner, while concurrent statements offer a more parallel execution approach. Welcome to this beginner's guide on VHDL basics, where we will dive into the concepts of sequential and concurrent statements in VHDL. If you've ever been confused about these fundamental aspects of VHDL programming, this video is perfect for you. We will start by explaining the differences between sequential and concurrent statements, providing clear examples and illustrations to eliminate any confusion. By the end of this video, you will have a solid understanding of how to effectively utilize sequential and concurrent statements in your VHDL designs. This guide is suitable for beginners who have some basic knowledge of VHDL. We will go step-by-step and explain each concept thoroughly, ensuring that you grasp the fundamentals before moving on to more advanced topics. Make sure to subscribe to our channel for more informative videos on VHDL programming and digital design. Don't forget to hit the notification bell to stay updated with our latest uploads. If you have any questions or suggestions, feel free to leave them in the comments section below.

#VHDL basics#VHDL programming#VHDL tutorial#VHDL sequential statements#VHDL concurrent statements#VHDL beginner's guide#VHDL programming guide#VHDL insights#VHDL concepts#VHDL design#digital design#beginner's tutorial#coding tutorial#VHDL for beginners#VHDL learning#VHDL syntax#VHDL examples#VHDL video tutorial#VHDL step-by-step#VHDL Examples#VHDL Coding#VHDL Course#VHDL#Xilinx ISE#FPGA#Altera#Xilinx Vivado#VHDL Simulation#VHDL Synthesis#Youtube

1 note

·

View note

Video

youtube

Introduction to Functions with RTL Code Example in Verilog and VHDL with...

0 notes

Text

Price: [price_with_discount] (as of [price_update_date] - Details) [ad_1] Verilog Digital System Design, 2/e, shows electronics designers and students how to apply verilog in sophisticated digital system design. Using over a hundred skill-building, fully worked-out, and simulated examples, this completely updated edition covers Verilog 2001, new synthesis standards, testing and testbench development, and the new OVL verification library. Moving from simple concepts to the more complex, Navabi interprets verilog constructs related to design stages and design abstractions, including behavioral, dataflow, and structure description. With emphasis on the concepts of HDLs. Clear specification and learning objectives at the beginning of each chapter and end-of-chapter problems focus attention on key points. Written by a HDL expert, the book provides: * Design automation with Verilog * Design with Verilog * Combinatorial circuits in Verilog * Sequential circuits in Verilog * Language utilities * Test methodologies * Verification * CPU design and verification MUST-HAVE CD INCLUDED * Verilog and VHDL simulators * Synthesis tools * Mixed-level logic and Verilog design environment * FPGA design tools and environments from Altera * Related tutorials and standards * All worked examples from the book, including testbench and simulationrun reports for every example * Complete CPU examples with Verilog code and software tools * OVL verification libraries and tutorials [ad_2]

0 notes

Text

Best VLSI Projects for Final Year Students

Here are some great VLSI project ideas for final-year students:

1. Image Processing System on FPGA: Algorithm, such as edge detection or image filtering should be performed through the usage of FPGAs for optimal performance.

2. Low-Power SRAM Design: Design and simulate a low-power Static Random Access Memory (SRAM) cell, targetting leakage and dynamic power dissipation.

3. Digital Signal Processor (DSP) Design: Design an example of a DSP that will allow a specific signal to be filtered or, for instance, undergo FFT.

4. Wireless Sensor Network (WSN) Protocol Implementation: Devise a VLSI based sensor node for wireless communication that will support protocols used in data transmission.

5. Reconfigurable Hardware Architecture: It is necessary to elaborate a box which is able to evolve in order to support several applications: in this context, it is possible to try to reconfigure parts of the hardware during the runtime according to the specific needs of the client application.

6. Cryptographic Hardware Accelerator: Propose and design a device for which you could use cryptographic algorithms or primitives including AES or RSA where optimization of both speed optimization and security is important.

7. System-on-Chip (SoC) Design: Selected h/w architects use Verilog or VHDL to design a including microcontroller, memory and other peripherals.

8. Artificial Neural Network (ANN) on FPGA: Devise a mini ANN for image recognition and other related work and optimally use the features of parallel processing provisioned by FPGAs.9. Automated VLSI Testing Tool: Design a testing and validation software system that has reduced time and eliminated errors in conducting tests of VLSI designs (Very Large Scale Integration).

10. Temperature Sensor with Data Logger: It will be a VLSI (Very Large Scale Integration) chip for measuring temperature and recording data, with the capability to display the data on a PC or a mobile connection.

All these project proposals present prospects to learn diverse aspects of VLSI design and implementation in addition to enhancing creativity. Choose one that you are interested in and which you can afford to do!

#vlsi#finalyear#verylargescaleintegration#VLSIDesign#engineeringstudents#studentsprojects#takeoffedugroup#takeoffprojects

0 notes

Text

5 Reasons for Using an Open Source Register Automation Tool | Agnisys

Register automation is an integral part of IP and SoC development. Long ago, design, verification, firmware, and documentation teams preferred doing register management manually or each team wrote their own scripts for limited automation. Later, companies started doing this automation at the organization level. Central scripts were written for register automation for design, verification, firmware, and documentation teams, but still each had their own specifications. This led to many iterations between these teams before different collaterals were all brought in sync. As design complexity grew, maintaining these scripts became difficult, and commercial EDA tools took their place. Simultaneously, many open source tools also cropped up that could be used for register automation. Although commercial tools have their own value proposition, open source tools also have their use cases. The five primary reasons why you might use open source tool are:

1. Cost

Open source EDA tools are typically free to use as there is no license fee, support fee, etc. You can just download, install, and get going. Generally, these tools are ideal for students, academicians, and perhaps small companies or cash-starved start-ups. If the cost to fix a bug in the final product developed using an open source tool is less than the cost of a commercial EDA tool for register automation, then it may be beneficial to opt for it.

For companies, there are a few more factors that affect the cost indirectly; experienced CAD engineers are required to integrate the tool in the production environment without any compatibility issues. Also, design and verification teams must be able to quickly ramp up on the tool to be able to churn out fully tested and verified designs faster in order to meet the shrinking market window. Some software engineers may also be needed to fix any issues or tailor the open source tool to meet unique requirements.

Considering all the above factors, if you can ensure that the total cost of ownership of an open source tool remains less, then the open source tool can turn out to be cost-effective for your organization.

If saving money on a commercial tool is more important than the money spent on finding bugs later in the development flow then you can perhaps go with the open source solutions.

2. Features

More options, more confusion! Fewer options, less confusion!

Generally, commercial EDA tools offer a comprehensive range of features and functionalities, including a rich set of special registers, a large number of properties for customization, etc. as they are developed and maintained by dedicated teams with extensive resources and customer interactions.

The open source tools may not support comprehensive features and functionality, but with fewer options you are not spoiled for choice. Assess the specific requirements of your project, including design complexity, input specification format (System RDL/IP-XACT/Excel/Document or a mix of these formats), required output collateral formats (Verilog, VHDL, System Verilog, UVM, HTML, PDF, Markdown, etc.), performance targets, and time-to-market constraints. Determine whether the features and capabilities of the open source tool align with these requirements.

With limited requirements you can be satisfied with a smaller set of features. For example, you may be using just one input specification format so you may not need a tool that supports a mix of formats. Similarly, you may require only design and verification collaterals, so why should you pay for other collaterals such as firmware, documentation, and custom outputs? Also, you may be working on FPGAs so ASIC related features could be of no use to you. You may be dealing with small and fairly simple designs so you may not require high performance features like clock-domain-crossing (CDC), functional safety, and so on. Working across teams and geography may not be important for you, rendering enterprise level features useless for you.

If you have simple register maps and don’t have any 3rd party IPs in IP-XACT and other formats, then open source may be enough for you.

3. DIY

Companies can start with the open-source software and set up a team of software engineers to modify the code for specific project requirements, tailoring the tools to fit the company's unique needs. The main challenge here is when updates of an open source software are released. It is usually a thrilling adventure into the unknown. Your engineering team may need to spend hours tinkering with config files and compiling the source to maintain compatibility with your production tool flow. Some previous features may suddenly disappear or be implemented differently as these tools are ever evolving. Merging your custom changes to open source code with new updates often requires a major and costly effort.

If hours spent tinkering with the output generation is not going to cause delay in the project and the cost of dedicating software engineers in developing, refining and maintaining the open source tool for several years is less than the cost of the commercial tools, then open source might be a possible solution.

4. Support

Many open-source projects have vibrant communities of users and developers who contribute to ongoing development, provide support, and share knowledge. While open source communities are there to help, you need to navigate through different forums for advice. Extensive documentation requires skills to extract the right information or else you can drown in the sea of available materials.

Support can be a weakness for open source tools. Troubleshooting is a costly affair, and often time consuming as well, delaying your critical project. There are no training programs, although there could be numerous tutorials available to help users learn the nitty gritty of the tools. This kind of community based approach to support can make troubleshooting a tedious task, affecting productivity, and risking your project success.

If time to market is not important for your project, then the absence of quick support may be acceptable.

5. Transparency, Scaling and Certification

With open source software, the code transparency can provide reassurance regarding security and reliability. Transparency may also expose vulnerabilities and critical flaws making these tools susceptible to attacks.

Open source tools also need to scale with your company’s evolving needs to support future innovation and competitiveness. Your company’s growth trajectory is linked to the evolution trajectory of the open source tool, which may be good enough for the short term but not suitable for long term strategy.

In certain industries, such as aerospace, automotive, and medical devices, regulatory compliance is critical. Companies making products in these domains do not have the luxury of using open source tools as they may not offer features and certifications to ensure compliance with industry standards and regulations.

Open source crowdsource development has its advantages but what happens when multiple users have conflicting requirements? One will always need a person to maintain the branch with their changes.

ISO 26262 certification requires that the tool vendor follows standard development processes to ensure tool quality, predictability, and fault management. If certification is not important or necessary then open source software can be used.

Conclusion

Open source register automation tools have their strengths and weaknesses. There are numerous use cases for these tools especially in academics, prototyping, and non-critical projects/products. However, many other industries and applications have requirements that can only be met with commercial register automation solutions. Open source tools may look cost-effective in the short term but, in the long term, the cost of ownership and the risk to the project outweighs the perceived benefits.

0 notes

Text

Intel FPGAs speed up databases with oneAPI and SIMD orders

A cutting-edge strategy for improving single-threaded CPU speed is Single Instruction Multiple Data (SIMD).

FPGAs are known for high-performance computing via customizing circuits for algorithms. Their tailored and optimized hardware accelerates difficult computations.

SIMD and FPGAs seem unrelated, yet this blog article will demonstrate their compatibility. By enabling data parallel processing, FPGAs can boost processing performance with SIMD. For many computationally intensive activities, FPGA adaptability and SIMD efficiency are appealing.

High-performance SIMDified programming

SIMD parallel processing applies a single instruction to numerous data objects. Special hardware extensions can execute the same instruction on several data objects simultaneously.

SIMDified processing uses data independence to boost software application performance by rewriting application code to use SIMD instructions extensively.

Key advantages of SIMDified processing include:

Increased performance: SIMDified processing boosts computationally intensive software applications.

Integrability: Intrinsics and dedicated data types make SIMDified processing desirable.

SIMDified processing is available on many current processors, giving it a viable option for computational speed improvement.

Despite its benefits, SIMDified processing is not ideal for many applications. Applications with minimal data parallelism will not benefit from SIMDified processing. It is a convincing method for improving data-intensive software applications.

SIMD Portability Supports Heterogeneity

SIMD registers and instructions make up SIMD instruction sets. SIMD intrinsics in C/C++ are the best low-level programming method for performance.

Low-level programming in heterogeneous settings with different hardware platforms, operating systems, architectures, and technologies is difficult due to hardware capabilities, data parallelism, and naming standards.

Specialized implementations limit portability between platforms, hence SIMD abstraction libraries provide a common SIMD interface and abstract SIMD functions. These libraries use C++ template metaprogramming and function template specializations to translate to SIMD intrinsics and potential compensations for missing functions, which must be implemented.

C/C++ libraries let developers construct SIMD-hardware-oblivious application code and SIMD extension code with minimum overhead. Separating SIMD-hardware-oblivious code with a SIMD abstraction library simplifies both sides.

This method has promoted many SIMD libraries and abstraction layers to solve problems:

Examples of SIMD libraries

Google Highway (open-source)

Xsimd (C++ wrapper for SIMD instances)

Such libraries allow SIMDified code to be designed once and specialized for the target SIMD platform by the SIMD abstraction library. Libraries and varied design environments suit SIMD instructions and abstraction.

Accelerating with FPGAs

FPGAs speed software at low cost and power. Traditional FPGAs required a strong understanding of digital design concepts and specific languages like VHDL or Verilog. FPGA-based solutions are harder to access and more specialized than CPU or GPU-based computing platforms due to programming complexity and code portability. Intel oneAPI changes this.

Intel oneAPI is a software development kit that unifies CPU, GPU, and FPGA programming. It supports C++, Fortran, Python, and Data Parallel C++ (DPC++) for heterogeneous computing to improve performance, productivity, and development time.

Since Intel oneAPI can target FPGAs from SYCL/C++, software developers are increasingly interested in using them for data processing. FPGAs can be used with SIMDified applications by adding them as a backend to the SIMD abstraction library. This allows SIMD applications with FPGAs.

SIMD and FPGAs go together Annotations let the Intel DPC++ compiler synthesis C++ code into circuits and auto-vectorize data-parallel processing. Annotating and implementing code arrays as registers on an FPGA removes data access constraints and allows parallel processing from sink to source. This enables SIMD performance acceleration using FPGAs straightforward and configurable.

SIMD abstraction libraries are a logical choice for FPGA SIMD processing. As noted, the libraries support Intel and ARM SIMD instruction set extensions. TSL abstraction library simplifies FPGA SIMD instruction implementation in the following example. The scalar code specifies loading registers, and the pragma unroll attribute tells the DPC++ Compiler to implement all pathways in parallel in the generic element-wise addition example below.

This simple element-wise example has no dependencies, and comparable implementations will work for SIMD instructions like scatter, gather, and store. Optimization can also accelerate complex instructions.

A horizontal reduction requires a compile-time adder tree of depth ld(N), where N is the number of entries. Unroll pragmas with compile-time constants can implement adder trees in a scalable manner, as shown in the following code example.

Software that calls a library of comparable SIMD components can expedite SIMD instructions on Intel FPGAs by adding the examples above.

Intel FPGA Board Support Package adds system benefits. Intel FPGAs use a BSP to describe hardware interfaces and offer a kernel shell.

The BSP enables SYCL Universal Shared Memory (USM), which frees the CPU from data transfer management by exchanging data directly with the accelerator. FPGAs can be coprocessors.

The pre-compiled BSP generates only kernel logic live, reducing runtime.

Intel FPGAs are ideal for SIMD and streaming applications like current composable databases because to their C++/SYCL compatibility, CPU data transfer offloading, and pre-compiled BSPs.

SIMD/FPGA simplicity At SiMoDSIGMOD 2023 in Seattle, USA, Dirk Habich, Alexander Krause, Johannes Pietrzyk, and Wolfgang Lehner of TU Dresden presented their paper “Simplicity done right for SIMDified query processing on CPU and FPGA” on using FPGAs to accelerate SIMD instructions. The work, supported by Intel’s Christian Färber, illustrates how practical and efficient developing a SIMDified kernel in an FPGA is while achieving top performance.

The paper evaluated FPGA acceleration of SIMD instructions using a dual-socket 3rd-generation Intel Xeon Scalable processor (code-named “Ice Lake”) with 36 cores and a base frequency of 2.2 GHz and a BitWare IA-840f acceleration card with an Intel Agilex 7 AGF027 FPGA and 4x 16 GB DDR4 memories.

First, they gradually increased the SIMD instance register width to see how it affected maximum acceleration bandwidth. The first instance, a simple aggregation, revealed that the FPGA accelerator’s bandwidth improves with data width doubling until the global bandwidth saturates an ideal acceleration case.

The second scenario, a filter-count kernel with a data dependency in the last stage of the adder tree, demonstrated similar behavior but saturates earlier at the PCIe link width. Both scenarios demonstrate the considerable speeding gains of natively parallel instructions on a highly parallel architecture and suggest that wide memory accesses could sustain the benefits.

Final performance comparisons compared the FPGA and CPU. CPU and FPGA received the same multi-threaded AVX512-based filter-count kernel. As expected, per-core CPU bandwidth decreased as thread count and CPU core count grew. FPGA performance was peak across all workloads.

Based on this work, the TU Dresden and Intel team researched how to use TSL to use an FPGA as a bespoke SIMD processor.

Read more on Govidhtech.com

0 notes

Note

I don't know much about VHDL so I can't really compare them, but its more C like but imo it's closer to like BASIC. it's also a bit lower level, I've heard. it's also a lot less verbose. for example, to implement a simple decade counter in verilog:

module decade_counter (clock, pulse);

input wire clock; // we take an input of the clock

reg [3:0] cntr; // define a 4 bit register

always @(posedge clock) begin // at each clock pulse...

cntr <= cntr + 1; // I normally use verilog 2001, but if you're using SystemVerilog you can use cntr++ here

if (cntr == 10)

cntr <= 0; // reset counter to zero once it reaches 10

end

output wire pulse; // 1 bit pulse output

assign pulse = (cntr == 0); // send a pulse out when cntr is reset to 0.

endmodule

NO WAY THERES AN HDL BLOG NOW

can we be besties I love FPGAs

more of a verilog guy tho sorry >///<

Yes we can be besties,

Now tell me about verilog!! I've never tried it, but heard it's more C-like? Is it nice?

4 notes

·

View notes

Text

Lightning Talk: AE Processor

AE Processor

EDIT: So I forgot my gifs were transparent... The input is just labelled 'plain text' for the encryption gifs, and the output is 'ciphertext'.

So... I decided to do a lightning talk because why not. It revolved around a custom processor I made for Computer Architecture which was capable of performing authenticated encryption (AE).

((I know I spelt cipher wrong, don't roast me.))

I find it wild that I requested to my lightning talk this week and it was coincidentally the same week we learn about block ciphers!!!

Also got a shout-out in an e-mail my tutor sent out YTB.

What We Had To Do

Given the bare bones of a MIPS processor, we had to modify the ISA to allow the processor to be capable of performing AE.

I know we were told DON'T ROLL YOUR OWN but hey, it's not like we were actually going to use this thing to encrypt sensitive information.

How It Works

There are two component: encryption and tag generation.

Encryption

This encryption scheme is a stream cipher, meaning that it encrypts one character at a time. It takes in one character at a time. It then XOR's the character with a byte of the encryption subkey, which is then input into an S-box in the form of an RN table based off the last 4 bits of the encrypted character at this point. This output is then XOR'ed with the next byte of the encryption key and then input into the S-box. This is done for a total of 8 rounds. (Wow I'm really trying to use the terminology from the AES activity)

Here's a gif I made last year. I know I spelt cipher wrong AGAIN, please forgive me.

The last step is to AND the encrypted character 0x7F (this was a given) to produce the final ciphertext.

Tag Generation

The last step is tag generation, to ensure the authenticity and integrity of the ciphertext.

One by one, each encrypted character is shifted depending on the MSB of the tag generation key. In the case of the given example below, the key is 1010. If the MSB is 1, the ciphertext is shifted twice to the left. This value is then XOR'ed with the previous cipher text and so on. After each XOR, the tag generation key is shifted once to the left so that it keeps rotating.

It can be noted that the first character is XOR'ed with 0x00, but this could be improved by adding in an initialisation vector. However, random number generation in VHDL is a pain, so it's a no from us.

Since this tag is generated using a private key, and is based off the original cipher text itself, it can guarantee authentication and integrity, just like a MAC... I guess this tag works similar to a MAC...

What We Did

So here's what the inside of a processor looks like.

It might look confusing, but bare with me.

The black lines are the data paths, and the orange are the control paths ie. the data channels and control channels are separate, such that an attacker is unable to input dodgy instructions to produce dodgy outputs (unless they get into the actual processor, which is a hurdle).

There is also a control path connecting the output of the registers with the ALU such that is is able to determine whether an XOR would result in an RN look-up or just a plain XOR result. What does this mean? Well, the way I implemented it was that the XOR for the encryption was done two at a time. Therefore the character was always XOR'ed with what seemed to be a 2 byte number. By checking whether the number was 2 bytes or less, the processor was able to determine whether to use an S-box or not.

I also find it interesting that logic operations such as XOR are used because it can easily be done in hardware. It was something I never really thought about before.

Results

For the keen beans, here are the results of encrypting 'CompArch'. The orange represents the resulting ciphertext, and the purple is the resulting tag. There is a long gap between 3F and 37 as M and P are both encrypted as 3F.

ie. CompArch -> 52 48 3F 3F 37 11 52 11

If you think I'm trolling, I verified my results using a program I made. It's not hardcoded I swear.

(Ignore the m and n. M referred to the number of rounds in encryption and the N referred to the number of bits to be shifted in tag generation. This was an extension to the core task)

4 notes

·

View notes

Text

youtube

VHDL Basics : Insights Sequential and Concurrent Statements - No More Confusion [Beginner’s Guide]

In this comprehensive tutorial, we will cover everything you need to know about VHDL sequential and concurrent statements. Sequential statements allow us to execute code in a step-by-step manner, while concurrent statements offer a more parallel execution approach. Welcome to this beginner's guide on VHDL basics, where we will dive into the concepts of sequential and concurrent statements in VHDL. If you've ever been confused about these fundamental aspects of VHDL programming, this video is perfect for you. We will start by explaining the differences between sequential and concurrent statements, providing clear examples and illustrations to eliminate any confusion. By the end of this video, you will have a solid understanding of how to effectively utilize sequential and concurrent statements in your VHDL designs. This guide is suitable for beginners who have some basic knowledge of VHDL. We will go step-by-step and explain each concept thoroughly, ensuring that you grasp the fundamentals before moving on to more advanced topics. Make sure to subscribe to our channel for more informative videos on VHDL programming and digital design. Don't forget to hit the notification bell to stay updated with our latest uploads. If you have any questions or suggestions, feel free to leave them in the comments section below.

Subscribe to "Learn And Grow Community"

YouTube : https://www.youtube.com/@LearnAndGrowCommunity

LinkedIn Group : https://www.linkedin.com/groups/7478922/

Blog : https://LearnAndGrowCommunity.blogspot.com/

Facebook : https://www.facebook.com/JoinLearnAndGrowCommunity/

Twitter Handle : https://twitter.com/LNG_Community

DailyMotion : https://www.dailymotion.com/LearnAndGrowCommunity

Instagram Handle : https://www.instagram.com/LearnAndGrowCommunity/

Follow #LearnAndGrowCommunity

#VHDL basics#VHDL programming#VHDL tutorial#VHDL sequential statements#VHDL concurrent statements#VHDL beginner's guide#VHDL programming guide#VHDL insights#VHDL concepts#VHDL design#digital design#beginner's tutorial#coding tutorial#VHDL for beginners#VHDL learning#VHDL syntax#VHDL examples#VHDL video tutorial#VHDL step-by-step#VHDL Examples#VHDL Coding#VHDL Course#VHDL#Xilinx ISE#FPGA#Altera#Xilinx Vivado#VHDL Simulation#VHDL Synthesis#Youtube

1 note

·

View note

Text

Oooh, nice! I forgot about acronyms with numbers like that!

I have since learned that a nested acronym is called a "macronym", and the wikipedia article for that suggests "RARS" and "VITAL" as possible contenders:

VITAL -> "VHDL Initiative Towards ASIC Libraries" VHDL -> "VHSIC Hardware Description Language" VHSIC -> "Very High Speed Integrated Circuit" ASIC -> "Application-specific integrated circuit"

VITAL -> "Very High Speed Integrated Circuit Initiative Towards Application-specific integrated circuit Libraries"

Ratio: 93/5 = 18.6 (not good enough)

RARS -> "Regional ATOVS Retransmission Service" ATOVS -> "Advanced TOVS" TOVS -> "TIROS operational vertical sounder" TIROS -> "Television infrared observational satellite"

So RARS -> "Regional Advanced Television Infrared Observational Satellite Operational Vertical Sounder Retransmission Service"

Ratio: 103/4 = 25.75 (better)

There are also apparently a lot of symbols in protein naming, so e.g. the NACHT protein domain technically has a whopping ratio of 39.8, but some of the expansions aren't actually acronyms or initialisms, like HET being short for the "heterokaryon incompatibility protein" domain:

NACHT -> "NAIP, C2TA, HET-E, TEP1" NAIP -> "NLR family apoptosis inhibitory protein" NLR -> "NOD-like receptor" NOD-like -> "nucleotide-binding oligomerization domain-like" C2TA -> "class 2 major histocompatibility complex transactivator" HET -> "Heterokaryon incompatibility protein" (the -E is just a classifier, AFAICT) TEP1 -> "Telomerase protein component 1"

NACHT -> "Nucleotide-binding oligomerization domain-like receptor family apoptosis inhibitory protein, class 2 major histocompatibility complex transactivator, Heterokaryon incompatibility protein E, Telomerase protein component 1"

Ratio: 199/5 = 39.8

But it's not entirely fair to even call NACHT an acronym, since it's not actually short for "NAIP, C2TA, HET-E, TEP1", those are just common examples of things in that domain.

XHR stands for "XML HTTP Request", where XML is the "eXtensible Markup Language" and HTTP is the "Hypertext Transfer Protocol", so the full expansion of XHR is "extensible markup language hypertext transfer protocol request", so those 3 letters expand to 56 letters (62 with spaces), and this got me wondering, there must be acronyms or initialisms with an even greater ratio of "expanded length"/"unexpanded length", but apart from recursive acronyms I can't think of longer examples.

Can anyone else think of any?

270 notes

·

View notes

Text

Some Gags Still Work Some Gags Still Work

Some Gags Still Work Some Gags Still Work

Not all rich folks, however simply certain ones who obviously have nothing higher to do with their money. I must say, that the flip flops with the little pom poms on them are the cutest, but if you think that is too frilly, you might at all times go together with the ones that have flowers on them. The 2 market leading companies are Xilinx and Altera. Quite big quantity of customers chooses Altera as a result of of higher growth software solutions evaluating to Xilinx. Altera is one other nicely-recognized market chief that provides Cyclone, Arria and Stratix collection. There are several market leaders that produce varied SPLD, CPLD and FPGA chips. As an example, the versatile flat-footed variety are discouraged from making use of Fitflops since of the induced instability within the footwear which can bring about accidents to the wearer. Recently, there has been a surge in the recognition of this kind of footwear.

While your dress will disguise the footwear out of your visitors, the consolation involved with these sneakers will keep a smile on your face all evening. The wealthy will probably be bizarre. I learn constantly the incredibly stupid issues that wealthy people send their cash on. Many rich folks have good goals, some egocentric whereas others strive to assist others. Most vendors (especially within the night time markets) are often open to barter, so it finally ends up being a very good talent to study. If most of your colleagues are working with VHDL it is likely that you'll start utilizing VHDL and vice versa. Verilog or VHDL programming languages are used while working with FPGA. Espadrilles are the right alternative for wearing to the beach. Then deliver your love of the beach life into probably the most personal occasion of your life -- your wedding. First we come to the beach. I've learn that the very first thing an artist does if a chunk doesn't promote, is to double the worth. If you are a student it is probably going that your first choise will likely be made by your university and also you meet one of those gadgets within the lab.

Sometimes certain individuals in this world have extra money than sense, and in case you are studying this and purchased one in every of these items, then with the current state of the economy shame on you. Not just are they genuinely low-cost, they are often obtained in a blended bag of fabrics, colours, and types. CPLD can handle much more logical elements and features that typical SPLD machine. FPGA has extra versatile architecture than CPLD has. Hardware structure and features of FPGA is completely defined by consumer, while microcontrollers has predefined construction and features (e.g. Eight digital I/O pins, four analog and and so forth). While programming with VHDL programmer should write extra code, it find yourself with many errors but it surely finally ends up with excellent outcome. Beth Huntington Pin one facet of the hook and loop fastener to the tip of the suitable facet of the towel, above the ribbon casing. It means, that the person decides how every pin needs to be used and so on. It means, that an engineer, can make FPGA to work as it is needed.

With awesome indoor water park facilities, you'll be able to be sure that the rain won't be a hindrance to your loved ones's fun. A tie and/or a dress jacket might be optionally available, but again you could need to go with the extra professional direction. 98 (greater than I'd ever pay), which might be designed to look like those of a homeless particular person, proper down to the very fact that they're partially made with duct tape. As talked about above, the type of Rainbow sandals that I normally wear are the double layer flip flops with large straps. You can put on it wherever you want because it suits the invoice perfectly irrespective of the occasion. Wholesale flip flops could make your really feel look actually neat and enticing when you are within the pedicure spa. Input/output blocks are linked with I/O pins on the package. The structure has three parts: logic blocks, interconnection blocks and input/output blocks. Logic blocks consists of LUTs (look-up-tables) and flip flops. The interconnection blocks permit to attach logic blocks collectively.

Interconnection also may be programmed. Flip flops can be worn to reinforce the seems any outfit on casual events. Flip flops do not give you any assist, but they do present a barrier between you and one thing harmful. See to it that the clothes offer you simple motion. This book qualifies in their free delivery provide. Shoe Clips Base - This is the metallic piece that the flower can be connected to. The same will happen with programming language choice. Wich language you choose? It's not essential wich language you select. Some time in the past a real language conflict was operating. It is difficult to tell which language to study (Verilog or VHDL). Some FPGAs will do better with VHDL and some with Verilog. Both VHDL and Verilog are HDLs used to explain digital and blended sign programs. If they are fabricated from the incorrect species of armadillo, they are going to curl up right into a ball once they feel threatened.

1 note

·

View note

Text

Price: [price_with_discount] (as of [price_update_date] - Details) [ad_1] Master the art of FPGA digital system design with Verilog and VHDLThis practical guide offers comprehensive coverage of FPGA programming using the two most popular hardware description languages―Verilog and VHDL. You will expand your marketable electronic design skills and learn to fully utilize FPGA programming concepts and techniques. Digital System Design with FPGA: Implementation Using Verilog and VHDL begins with basic digital design methods and continues, step-by-step, to advanced topics, providing a solid foundation that allows you to fully grasp the core concepts. Real-life examples, start-to-finish projects, and ready-to-run Verilog and VHDL code is provided throughout. • Concepts are explained using two affordable boards―the Basys 3 and Arty • Includes PowerPoint slides, downloadable figures, and an instructor's solutions manual • Written by a pair of experienced electronics designers and instructors ASIN : 1259837904 Publisher : McGraw Hill; 1st edition (5 October 2017) Language : English Hardcover : 400 pages ISBN-10 : 9781259837906 ISBN-13 : 978-1259837906 Item Weight : 903 g Dimensions : 19.3 x 2.54 x 24.13 cm Country of Origin : USA [ad_2]

0 notes

Text

Qucs switch simulation

QUCS SWITCH SIMULATION SOFTWARE

QUCS SWITCH SIMULATION SIMULATOR

QUCS SWITCH SIMULATION DOWNLOAD

A modern meshless autorouter is capable of efficiently and quickly routing both complex multilayer boards with different types of components, and simple two-layer projects.

The Arrange, List Positioning, and Automatic Component Arrangement features help you quickly and easily optimize component placement and board dimensions.

Layered hierarchy and support for multi-sheet boards allow you to quickly and efficiently develop complex schematic drawings.

QUCS SWITCH SIMULATION SOFTWARE

It is also a software for building circuit simulation. The purpose of these exercises is not to learn wiring diagrams, but to practice working with the program. Students are encouraged to solve these problems in order to compare the answers received with those given in the book. They show the schematic and the results obtained during the simulation, when to run the circuit. Proposed solutionThere are exercises at the end of each section. These books collect the most interesting ideas of useful devices, giving every radio amateur the opportunity to choose what he needs from a great variety of solutions and designs on the a3144 hall sensor, tested and tested in practice. We need this software for simulation modeling of radio engineering structures. Radio engineering programs are useful for radio amateurs. Tags: Software for designing modeling of schematic solutions is presented here. Program for tracing printed circuit boards Just click with the cursor on the required element of the diagrams. The graph of the change in the current through the element of the device, follows The graph will show the change in potential at this point When we click with the cursor on the required wire on the circuit elements, In simulation mode, a half-screen graph will open. Specify the time for calculating Stop Time, for example 25m (25ms). Simulate-> Edit Simulation Cmd in Transient Tab It is very easy to draw radio circuits in it - interfaceĪ program for the compilation of electronic projects.īefore starting the simulation mode, do not forget in the menu

QUCS SWITCH SIMULATION SIMULATOR

Nice handy simulator of electronic circuits. The distribution kit includes a visual presentation.Ī program for creating electronic circuits. It also includes the ability to lay out printed circuit boards. In the form of a 3D finished device and graphs of transients. Simulation software for radio circuits with visual

QUCS SWITCH SIMULATION DOWNLOAD

the ability to download additional interface languages.open source allows you to develop extensions.pre-compiled VHDL modules and libraries.support for equations for Verilog-HDL and VHDL subchains.support for syntax Verilog-HDL and Verilog-A in text documents.Recent versions of Qucs have the GNU / Octave interface. The program has support for exporting symbol images with Verilog-A files to C ++ code, support for direct communication with Verilog-HDL symbols and VHDL sub-chains. It was created by default to work with the Qucs project, but it can be used with other applications as well. Qucsator, the back end of the program, is a command line simulator that manages the list of networks for a specific I / O format of the Qucs dataset. The simulation results can be viewed on the presentation page or the program window. The program supports all kinds of circuit simulation, such as DC, AC, S-parameters, harmonic balance analysis, noise analysis and so on. Qucs, also known as Quite Universal Circuit Simulator, was designed to be an affordable open source, graphical and graphical electronic circuit and circuit simulator.

0 notes

Text

8 bit parallel to serial converter ic

#8 BIT PARALLEL TO SERIAL CONVERTER IC SERIAL#

#8 BIT PARALLEL TO SERIAL CONVERTER IC UPDATE#

#8 BIT PARALLEL TO SERIAL CONVERTER IC CODE#

I mean, if the parallel data is not yet totally serialized, no other input data can be processed. The error detection logic rises the “ o_error_serialize_pulse” if the input data enable is high during the serialization process.

#8 BIT PARALLEL TO SERIAL CONVERTER IC CODE#

In the VHDL code is implemented an error detection logic. Signal r_data : std_logic_vector(G_N-1 downto 0) O_error_serialize_pulse : out std_logic) I_data : in std_logic_vector(G_N-1 downto 0)

#8 BIT PARALLEL TO SERIAL CONVERTER IC SERIAL#

Figure 2 Parallel to Serial conversion exampleĪn example of Parallel to Serial converter The serializer section takes N clock cycles to output the serial data stream. The parallel input to the module shall be at a rate of less than or equal to 1/N clock cycles. Let assume the parallel data bus of the Parallel to Serial converter to be N bit. Parallel to Serial converter VHDL code example If you need to transfer 16-bit data 1MHz the serial data stream speed shall be at least greater than 16 x 1 MHz = 16 MHz. Same data rate you need to use a higher speed in data transfer. Figure 1 FPGA connection Parallel vs SerialĬould be to serialize the parallel data using less connection. As you can see, these are a lot of wires! Moreover, a skew between the bits in the parallel data bus can affect the connection integrity. For instance, if we need to transfer a data bus of 16 bits between twoĭifferent FPGA at a rate of 1 MHz, we need to connect at leastġ6-bit data + 1 bit enable + 1 bit clock = 18 wires running 1 MHz. This way the first 8-bit sent from MCU will be used by the 1st IC and the second 8-bit will be used by the 2nd IC.From two different devices, the simple way is to use the minimum numbers of To do this, we use the Q7’ (pin 9), this pin should be connected to the data pin of the second 74HC595 IC. The pin Master reset (MR) is used to reset the outputs, when not in use it is held high to vcc, similarly the pin should be held low when not in use.Īnother important advantage of the 74hc595 IC is that it can be cascaded to control more than 8 outputs. Here for example the binary value 0b10110011 is passed to the microcontroller. The Pin 12 is the Latch which updates the received the data to the output pins when made high, this pin can also be permanently held high. The below image will help you understand better.Īs you can see the clock is continues train of pulses, and the data goes high only at the respective place where the output has to get high. The pin 14 is Data which actually sends the Data about which output pins has to stay low and which should go high. In which pin 11 is the clock which sends a constant pulse to keep timing. The pins 11, 14 and 12 are connected to the GPIO pins of the Microcontroller. An application circuit of the IC is shown below: It has a wide operating voltage from 2V to 6V. It requires only 3 pins connected to the MCU, which are Clock, Data, and Latch. The 74HC595 shift register is commonly used with microcontrollers or microprocessors to expand the GIPO functionalities. So if you are looking for an IC to save on your GPIO pins on the Microcontroller, then this IC might be the right choice for you. It can also be used to control 5V loads like relays through a 3.3V microcontroller since the high-level voltage is only 3.15. It can also be used to interface LCD screen since they can acts as the data bit for the LCD displays. It is often used in projects where relatively a large number of LED’s has to be controlled through the Microcontroller. This comes in very handy where do not have enough GPIO pins on our MCU/MPU to control the required number of outputs. it can receive (input) data serially and control 8 output pins in parallel. The 74HC595 is an 8-bit Serial In – Parallel Out Shift Register, i.e. Note: Complete technical details can be found in the 74HC595 datasheet given at the end of this page.Ĥ-Bit Parallel in Parallel out Shift Register Maximum Clock Frequency: 25Mhz Available in 16-pin PDIP, GDIP, PDSO packages.Minimum high-level Input Voltage: 3.15V Maximum low-level Input Voltage: 1.35V Can be easily cascaded with more IC to get more outputs.Output Voltage is equal to Operating voltage.8-bit, Serial In – Parallel out Shift register.This pin powers the IC, typically +5V is used. This is the pin to which data is sent, based on which the 8 outputs are controlled The Output Enable is used to turn off the outputs.

#8 BIT PARALLEL TO SERIAL CONVERTER IC UPDATE#

The Latch pin is used to update the data to the output pins. This is the clock pin to which the clock signal has to be provided from MCU/MPU This pin is used to connect more than one 74hc595 as cascading The 74hc595 has 8 output pins out of which 7 are these pins.

0 notes

Text

Xilinx ise 14.7 windows 10 pn.exe error

It strongly supports code reusability and code sharing.Ī list of disadvantages of VHDL is given below:.

It provides tight coupling to lower levels of design.

It provides a flexible design language.

It supports various design methodologies like Top-down approach and Bottom-up approach.

For early performance estimation of system architectureĪ list of advantages of VHDL is given below:.

2008: IEEE Standard 1076-2008 (New features) was released.

1999: Analog Mixed Signal extension (VHDL-AMS).

1996: A VHDL package used with synthesis tools and became a part of the IEEE 1076 standard.

1993: VHDL was re-standardized to enhance the language.

1987: DOD permitted for commercial purpose, and VHDL became IEEE Standard 1076-1987.

1985 (VHDL Version 7.2): The final version of the language under the government contract was released.

1983: The development of VHDL began with a joint effort by IBM, Inter-metrics, and Texas Instruments.

1980: The Department of Defence wanted to make circuit design self-documenting.

VHDL was developed by the Department of Defence (DOD) in 1980. It does not support the Multi-Dimensional array. It does not allow the user to define data types. The most popular examples of Verilog are network switch, a microprocessor, a memory, a simple flip-flop, etc. It is used in both hardware simulation and synthesis. Verilog is also a HDL (Hardware Description Languages) for describing electronic circuits and systems.

Design methodologies and their features.

The most popular examples of VHDL are Odd Parity Generator, Pulse Generator, Priority Encoder, Behavioral Model for 16 words, 8bit RAM, etc. It is an IEEE (Institute of Electrical and Electronics Engineers) standard hardware description language that is used to describe and simulate the behavior of complex digital circuits.

VHDL stands for Very High-Speed Integration Circuit HDL (Hardware Description Language). Today, there are many HDLs available in the market, but VHDL and Verilog are the most popular HDLs.

The main advantage of HDLs is that it provides flexible modeling capabilities and can express the large complex designs (>10 7 gates). HDL is mainly used to discover the faults in the design before implementing it in the hardware. It is a programming language that is used to describe, simulate, and create hardware like digital circuits (ICS). HDL stands for Hardware Description Language.

Creating a Project in VHDL using the Xilinx IDE tool.

Our VHDL tutorial is designed for beginners and professionals. VHDL tutorial provides basic and advanced concepts of VHDL.

0 notes

Text

Qucs switch simulation

#QUCS SWITCH SIMULATION HOW TO#

The transmission line calculator can be used to design and analyze different types of transmission lines (e.g. SPICE netlists, or Touchstone files).Ī filter synthesis application can help design various types of filters. It is handy to edit files related to certain components (e.g. The GUI includes a text editor which can display netlists and simulation logging information. It reads a netlist file augmented with commands, performs simulations, and finally produces a dataset file. The analog simulator, gnucsator, is a command line program which is run by the GUI in order to simulate the schematic which you previously setup. The GUI is used to create schematics, setup simulations, display simulation results, writing VHDL code, etc. Qucs consists of several standalone programs interacting with each other through a GUI. Other features include the transmission line calculator, Filter synthesis, Smith-Chart tool for power and noise matching, Attenuator design synthesis, Device model and subcircuit library manager, Optimizer for analog designs, the Verilog-A interface, Support for multiple languages ( GUI and internal help system), Subcircuit (including parameters) hierarchy, Powerful data post-processing possible using equations and symbolically defined nonlinear and linear devices. The documentation offers many useful tutorials (WorkBook), reports (ReportBook) and a technical description of the simulator. Simulation data can be represented in various types of diagrams, including Smith-Chart, Cartesian, Tabular, Polar, Smith-Polar combination, 3D-Cartesian, Locus Curve, Timing Diagram and Truth Table. Qucs has a graphical interface for schematic capture. The course contains theoretical video classes with examples, quizzes, and an entire set of simulation files, step-by-step procedures, recorded data of real-life circuits, and solution videos so that students can learn from and build even better circuits.Analysis types include S-parameter (including noise), AC (including noise), DC, Transient Analysis, Harmonic Balance (not yet finished), Digital simulation (VHDL and Verilog-HDL) and Parameter sweeps. But ultimately, this would allow students to design and build their own transceiver at home! The other 30% will require students to either get access to an electronics lab or to purchase a few off-the-shelf components. The design labs are completely optional for obtaining the certificate, but they are recommended because they allow students to put into practice all the acquired theoretical knowledge, and of course, implementing the circuits is where all the fun is! The students will be able to do 70% of the design labs using simulation tools, which already offers a great learning experience. It is divided into two parts: (1) theoretical lectures will cover the basis of RF and mmWave Circuit Design and (2) design labs will include simulation and implementation of these circuits.

#QUCS SWITCH SIMULATION HOW TO#

The course covers the topics on how to derive the RF wireless systems specifications, and how to design the main building blocks of a transceiver, i.e., low noise amplifier, power amplifier, RF mixers, oscillators, and PLL frequency synthesizers. This unique Master-level course offered by the Center for Wireless Technology Eindhoven (CWT/e) of the Eindhoven University of Technology, The Netherlands, provides students with in-depth knowledge and hands-on experience on RF and mmWave circuit design.

0 notes